# AUTOMATED INTEGRATION OF SIMULINK MODELS INTO VIRTUAL PLATFORMS

ANDREAS MAUDERER ROBERT BOSCH GMBH – AUTOMOTIVE ELECTRONICS

ALEXANDER SCHREIBER THE MATHWORKS GMBH

MATLAB EXPO JUNE 27<sup>TH</sup>, 2017 MUNICH, GERMANY

This work has been funded by the German Federal Ministry for Education and Research (BMBF) under the grant 01IS13022A (project EffektiV). The content of this publication lies within the responsibility of the authors.

BOSCH

Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

© Robert Bosch GmbH 2017. All rights reserved, also regarding any disposal, exploitation, reproduction, editing, distribution, as well as in the event of applications for industrial property rights.

BOSCH

Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

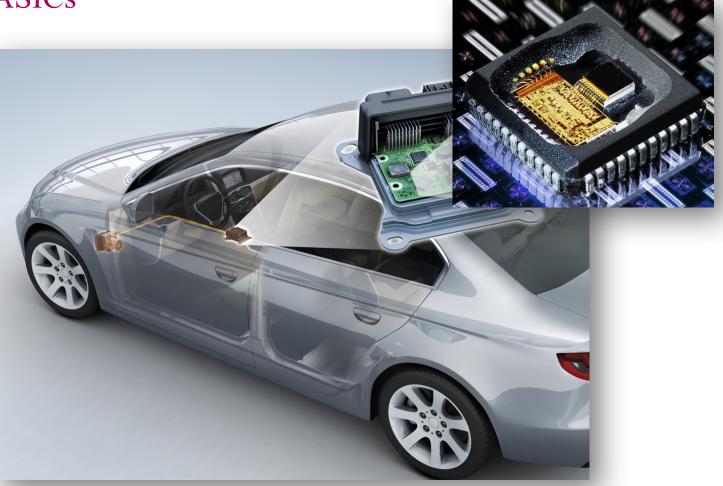

# Integration of Simulink Models into Virtual Platforms Automotive Mixed-Signal ASICs

- Bosch accelerates progress of automotive technology with continued innovations like ESP or autonomous driving solutions

- Integral part for these solutions are automotive sensors

- Example: Inertial sensor system for ESP

Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017 © Robert Bosch GmbH 2017. All rights reserved, also regarding any disposal, exploitation, reproduction, editing, distribution, as well as in the event of applications for industrial property rights.

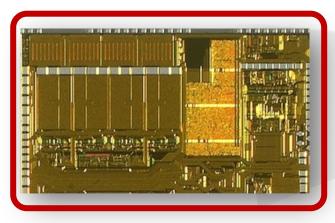

# Integration of Simulink Models into Virtual Platforms Automotive Mixed-Signal ASICs

- ► Heterogeneous SoC:

- ► Analog Hardware

- Digital Non-Programmable Hardware

- ► Processors

Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017 © Robert Bosch GmbH 2017. All rights reserved, also regarding any disposal, exploitation, reproduction, editing, distribution, as well as in the event of applications for industrial property rights

► System-in-Package (SiP)

BOSCH

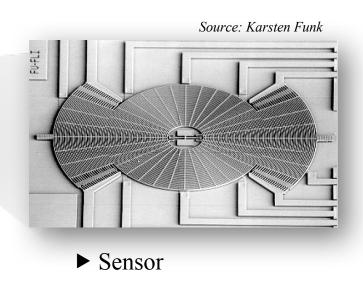

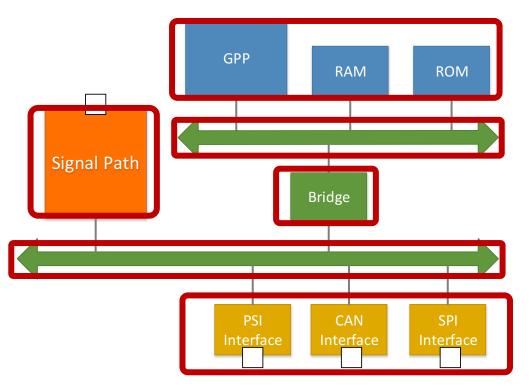

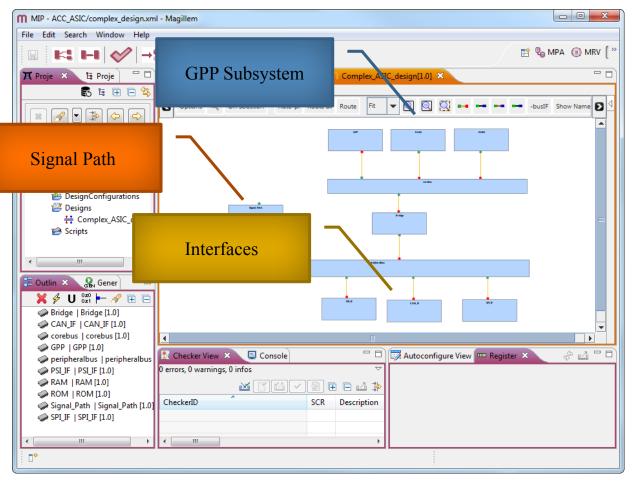

Integration of Simulink Models into Virtual Platforms Sensor ASIC – Architecture Example

- Signal path for sensor signal processing

- General Purpose Processor (GPP) subsystem for

- ► safety monitoring

- communication protocols

- ► etc.

6

Several interfaces

► On-Chip Architecture

Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017 © Robert Bosch GmbH 2017. All rights reserved, also regarding any disposal, exploitation, reproduction, editing, distribution, as well as in the event of applications for industrial property rights

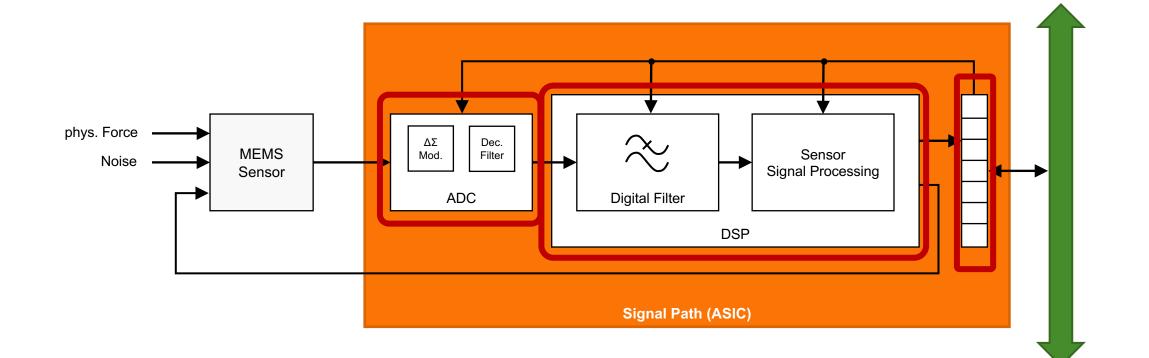

## Integration of Simulink Models into Virtual Platforms Sensor ASIC – Signal Path Example

#### Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

0

Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017 © Robert Bosch GmbH 2017. All rights reserved, also regarding any disposal, exploitation, reproduction, editing, distribution, as well as in the event of applications for industrial property rights.

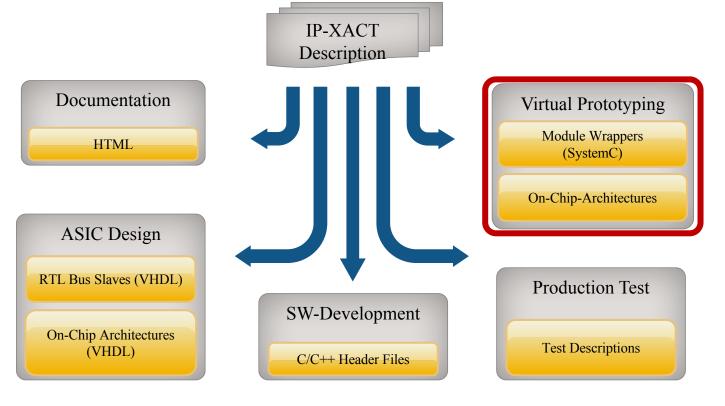

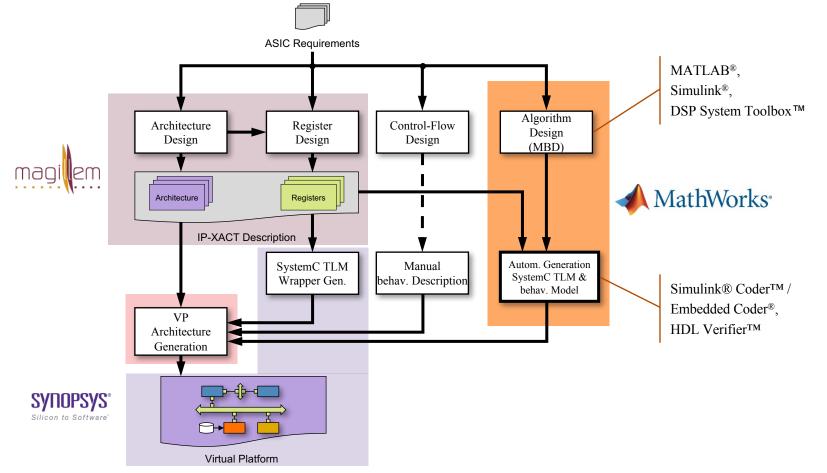

Integration of Simulink Models into Virtual Platforms Current Workflow - IP-XACT-Centric Tool Environment

- ► IP-XACT description as single source

- Generation of various design, test and documentation outputs

- Ensures consistency throughout the whole design flow

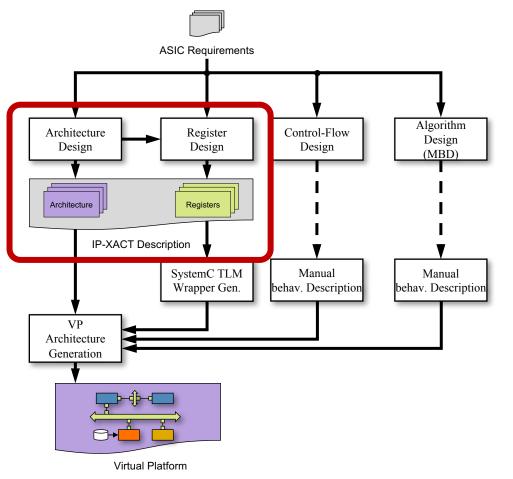

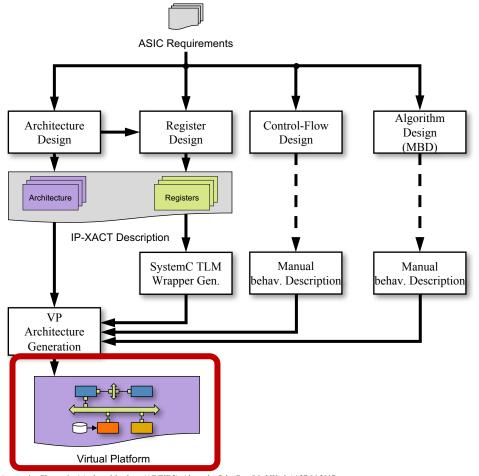

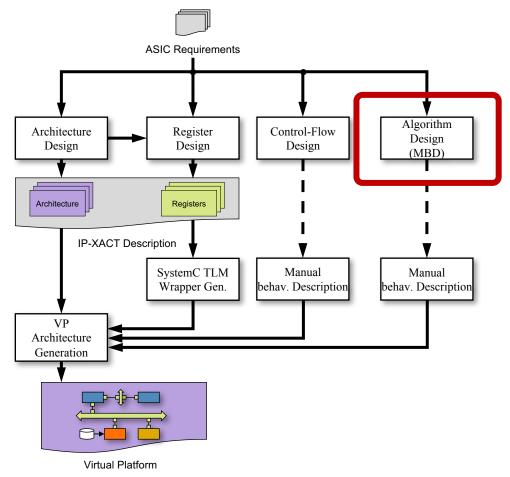

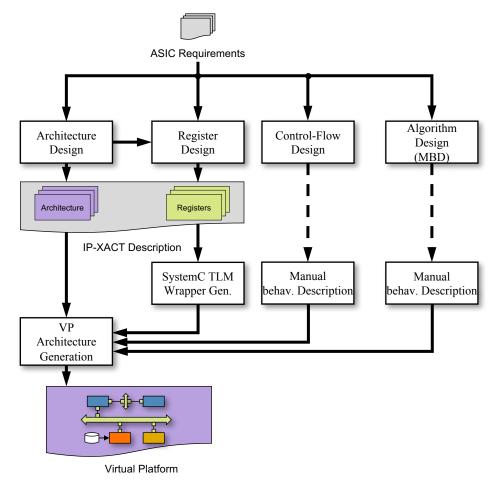

# Integration of Simulink Models into Virtual Platforms Current Workflow - IP-XACT-Centric VP Generation

- Description of architecture and register interfaces in IP-XACT

- Automated generation of VP architectures and TLM register interfaces

- Signal processing algorithm design using Model-Based Design

- Manual behavioural description of controland signal-flow oriented designs

Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

# Integration of Simulink Models into Virtual Platforms Architecture Design - Magillem<sup>®</sup> IP-XACT Packager (MIP)

- Design of On-Chip Architecture in Magillem<sup>®</sup> IP-XACT Packager

- Saved as IP-XACT Design description

1 Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

# Integration of Simulink Models into Virtual Platforms Register Interface Design - Magillem<sup>®</sup> Register View (MRV)

- Design of register interfaces in Magillem<sup>®</sup> Register View

- Saved as IP-XACT Component description

| MRV - ACC_ASIC/Signal_Path.xml - Magillem |                                |                      |             |                  |                      |  |  |  |

|-------------------------------------------|--------------------------------|----------------------|-------------|------------------|----------------------|--|--|--|

| File Edit Search Model Editor Window Help |                                |                      |             |                  |                      |  |  |  |

|                                           |                                |                      |             |                  | 😭 🌯 MPA 💽 MRV : »    |  |  |  |

| 🕱 Project 🗙 🗄 Project Hierar 📄 🗖          | Complex_ASIC_design[ 💦 🗰 S     | ignal_Path [1.0] 🙁   | »»2         | - 8              | 🔲 Pro 🗙 🔲 Sys 🖳 🗆    |  |  |  |

| 🛃 🗄 🕀 🕞 🤹                                 | Component: [Mathworks.com, MWT | LM, Signal_Path, 1.0 |             |                  | 표 🗦 💀 🛃 🏹            |  |  |  |

|                                           | memorymap_sensor               |                      |             |                  | Prop Value           |  |  |  |

| 💥 🔗 all 🔻 🍰 🗘 🖒                           | Search:                        | ۹. +                 | → RE 000    |                  | Prop Value           |  |  |  |

| ACC_ASIC                                  | Name*                          | Absolute Address     | Access Type | Address Offset*  |                      |  |  |  |

| AbstractionDefinitions                    | SensorInterface_AdressBlock    | 0x0 (computed)       |             | 0x00000000 (auto |                      |  |  |  |

| Abstractors                               | IIII ACC_1_In                  | 0x0 (computed)       | write-only  | 0x0              |                      |  |  |  |

| 🕮 BusDefinitions                          | MWMapInput                     |                      |             |                  |                      |  |  |  |

| 🔺 🔛 Components                            | ACC_2_In                       | 0x8 (computed)       | write-only  | 0x8              |                      |  |  |  |

| 🧼 Bridge [1.0] 🗏                          | MWMapInput                     |                      |             |                  |                      |  |  |  |

| CAN_IF [1.0]                              |                                |                      |             |                  |                      |  |  |  |

| i corebus [1.0]                           |                                |                      |             |                  |                      |  |  |  |

| 🧼 GPP [1.0]                               |                                |                      |             |                  |                      |  |  |  |

| i peripheralbus [1.0]                     |                                |                      |             |                  |                      |  |  |  |

| PSI_IF [1.0]                              |                                |                      |             |                  |                      |  |  |  |

| AAM [1.0]                                 |                                |                      |             |                  |                      |  |  |  |

| ROM [1.0]                                 |                                |                      |             |                  |                      |  |  |  |

| 🧼 Signal_Path [1.0] 👻                     |                                |                      |             |                  |                      |  |  |  |

| ۰ III +                                   | Memory Map Tree Table          |                      |             |                  |                      |  |  |  |

| 🔚 Outline 🗙 🚱 Generators 📃 🗆              | 🚥 Register 🗙 📮 Console 🔝       | Checker View         |             |                  | 🕹 🗖 🗖                |  |  |  |

| 🔚 Signal_Path 🔺                           |                                |                      |             | ACC_1_In         | ACC_1_In Description |  |  |  |

| MWVendor                                  |                                |                      |             |                  |                      |  |  |  |

| MWVersion                                 | 31 23                          | 15                   | 7           | <u> </u>         |                      |  |  |  |

| MWModel                                   |                                |                      |             | С <sup>1</sup>   | Bitfield Description |  |  |  |

| MWBlock                                   |                                |                      |             |                  |                      |  |  |  |

| memorymap_sensor                          |                                |                      |             |                  |                      |  |  |  |

| SensorInterface_AdressBlock               |                                |                      |             |                  |                      |  |  |  |

| ACC_1_In                                  | 1                              |                      |             |                  | •                    |  |  |  |

| □◆                                        |                                |                      |             |                  |                      |  |  |  |

|                                           |                                |                      |             |                  |                      |  |  |  |

Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

Integration of Simulink Models into Virtual Platforms Current Workflow - IP-XACT-Centric VP Generation

Automated generation of VP architectures and TLM register interfaces

Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

14

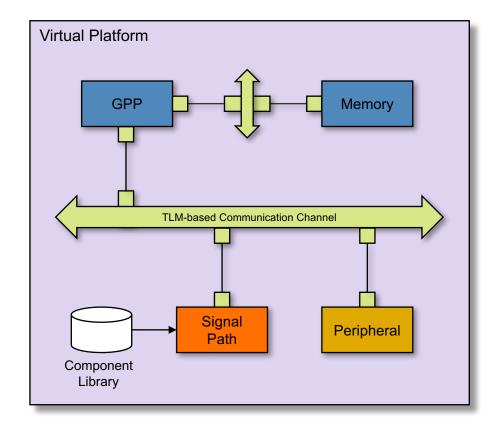

# Integration of Simulink Models into Virtual Platforms Virtual Platforms (VP)

- ► SoC architecture-centric

- Highspeed pre-silicon development environment

- Abstracting communication interfaces through Transaction Level Modelling (TLM)

## ► Benefits

- SoC concept validation and architectural exploration

- ► Concurrent SW and HW development

- ► Validation of HW/SW interfaces

- ► Optimization of SW

Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017 © Robert Bosch GmbH 2017. All rights reserved, also regarding any disposal, exploitation, reproduction, editing, distribution, as well as in the event of applications for industrial property rights.

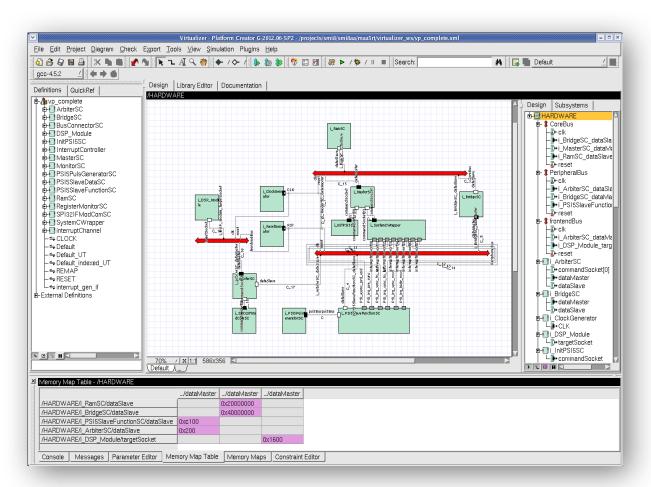

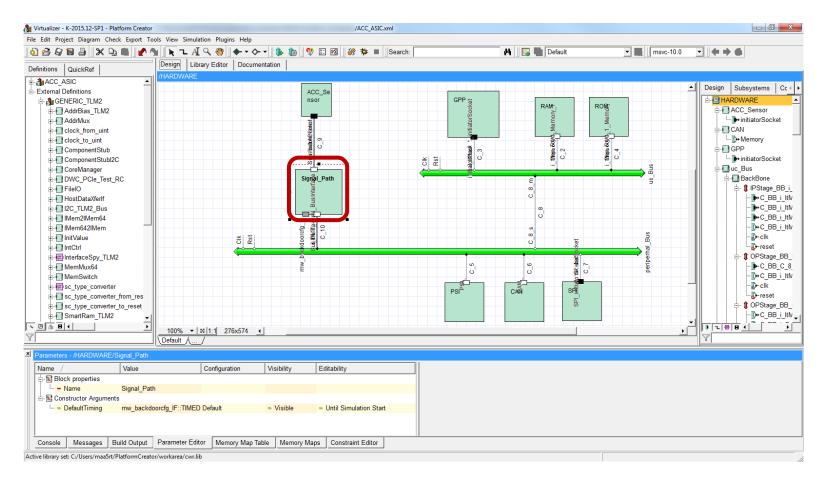

# Integration of Simulink Models into Virtual Platforms System Simulation and SW Dev. in Synopsys<sup>®</sup> Virtualizer<sup>TM</sup>

- Tool for construction and simulation of Virtual Prototypes

- ► Large module library

- ► Comprehensive debugging capabilities

- Export of development kits for SW development

## 16 Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

# Integration of Simulink Models into Virtual Platforms Current Workflow - IP-XACT-Centric VP Generation

Signal processing algorithm design using Model-Based Design

17 Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

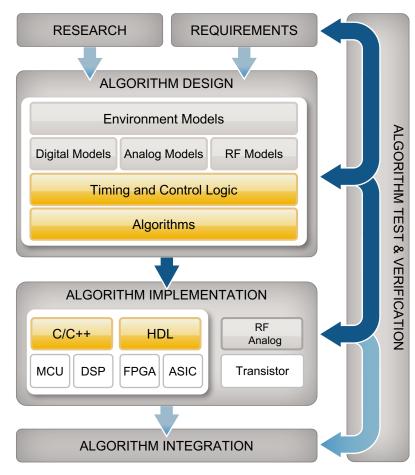

# Integration of Simulink Models into Virtual Platforms Model-Based Design (MBD)

- ► Algorithm-centric

- ► Signal flow-oriented multi-domain simulation

- Differential equation, transfer function, physical network level

- ► Time-continuous, time-discrete

- ► Value-continuous, value-discrete

- ► Benefits

- Mathematical algorithm design

- Early verification of its functional correctness and performance in its environment

- ► Implementation through automatic code generation

### Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

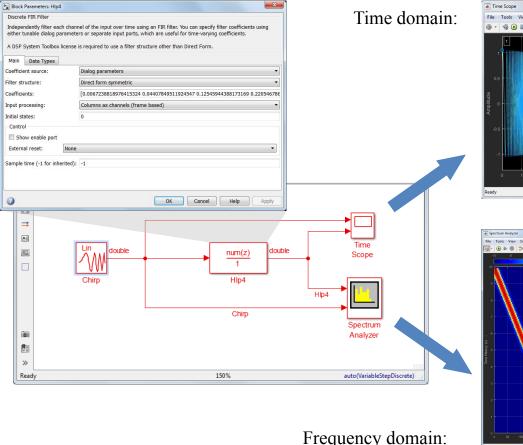

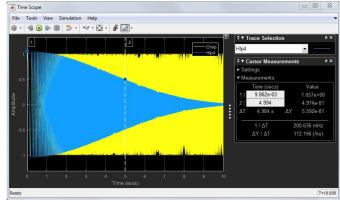

# Integration of Simulink Models into Virtual Platforms Example: Lowpass Filter Design with DSP System Toolbox<sup>™</sup>

Specification:

- ► Filter response: FIR

- Design Method: Equiripple

- ► 6dB-cutoff frequency: (.25

- ► Stopband attenuation: 6) dB

- ► Passband ripple: 1dB

| A Lowpass Design                                                |   |

|-----------------------------------------------------------------|---|

| Lowpass Design                                                  |   |

| Design a lowpass filter.                                        |   |

| Filter output variable name: Hlp4 View Filter Response          | e |

| Main Data Types Code Generation                                 |   |

| -Filter specifications                                          |   |

| Impulse response: FIR 🔹                                         |   |

| Order mode: Specity                                             |   |

| Order: 8                                                        |   |

| Filter type: Single-rate                                        |   |

| Frequency specifications                                        |   |

| Frequency constraints: Cutoff (6dB) frequency                   |   |

| Frequency constrained (out of 1)                                |   |

| Cutoff (6dB) frequency: .25                                     |   |

| Magnitude specifications                                        | 4 |

|                                                                 |   |

| Magnitude constraints: Passband ripple and stopband attenuation |   |

|                                                                 |   |

| Passband ripple: 1 Stopband attenuation: 60                     |   |

| Algorithm                                                       |   |

| Design method: Equiripple                                       |   |

| Pesigir options                                                 |   |

| Filter implementation                                           |   |

| Structure: Direct-form symmetric FIR                            |   |

| Use a System object to implement filter                         |   |

|                                                                 | 4 |

| OK Cancel Help Apply                                            |   |

1 Q Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

# Integration of Simulink Models into Virtual Platforms Signal-Flow-based Simulation with Simulink<sup>®</sup>

## 2.0 Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

# Integration of Simulink Models into Virtual Platforms Gap Analysis

- ► Benefits of Model-Based Design

- Verified algorithm meeting signal processing characteristics

- ► Workflow Gap

- Manual behavioural description of algorithm

- Manual integration into SystemC TLM wrapper

- ► Potential Issue

- Mismatch between manual behavioural description and implementation

21 Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

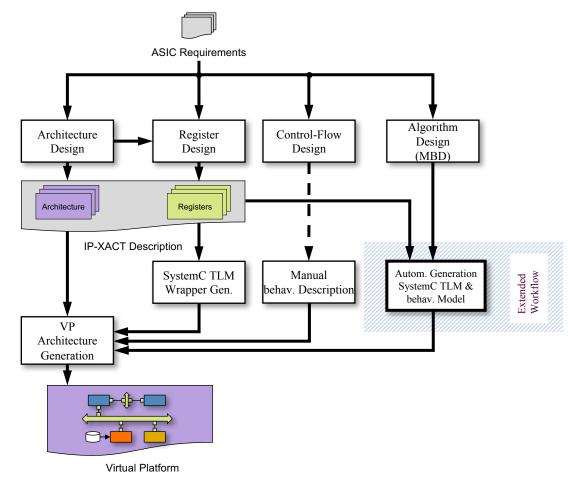

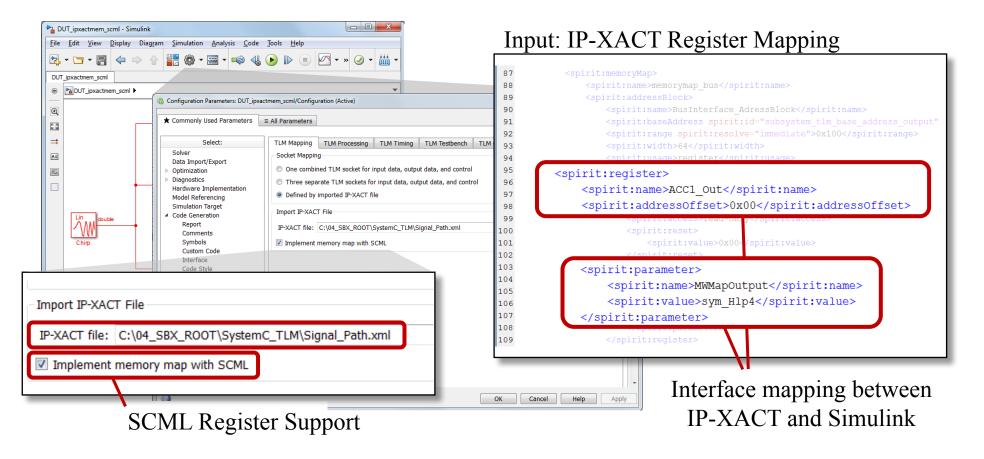

# Integration of Simulink Models into Virtual Platforms Gap Analysis

## Solution:

- Automatic generation of SystemC TLM component

- ► Behavioural algorithmic model

- ► Integration in SystemC TLM wrapper

- ► IP-XACT register definition as input

## ► Support of SCML register

77 Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

2.4 Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

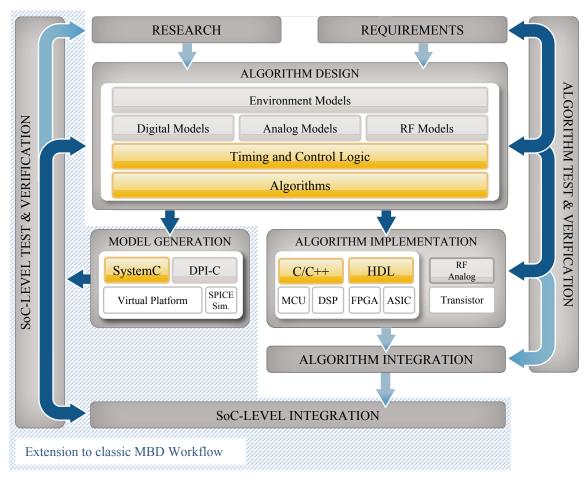

# Integration of Simulink Models into Virtual Platforms Algorithm Design & Model Generation

- Extended Model-Based Design Workflow

- Model Generation

- Additional code generation targets

- ► Virtual platforms (e.g. SystemC TLM 2.0)

- Verification environments (e.g. SystemVerilog DPI-C)

- ► Benefits

- ► Integrated, automated workflow

- ► Functional equivalence between ...

- Algorithm design

- Virtual Platform model

- Algorithm implementation

### 25 Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

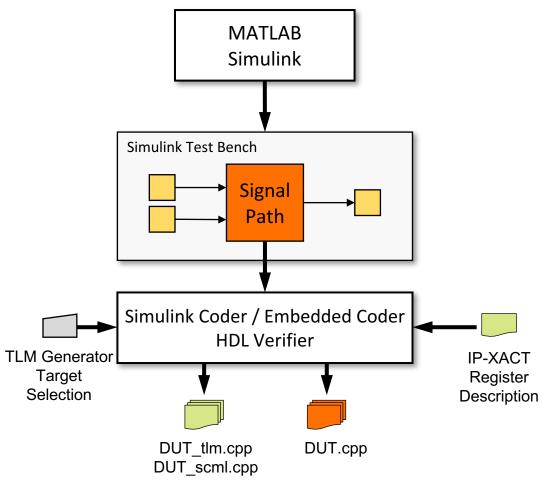

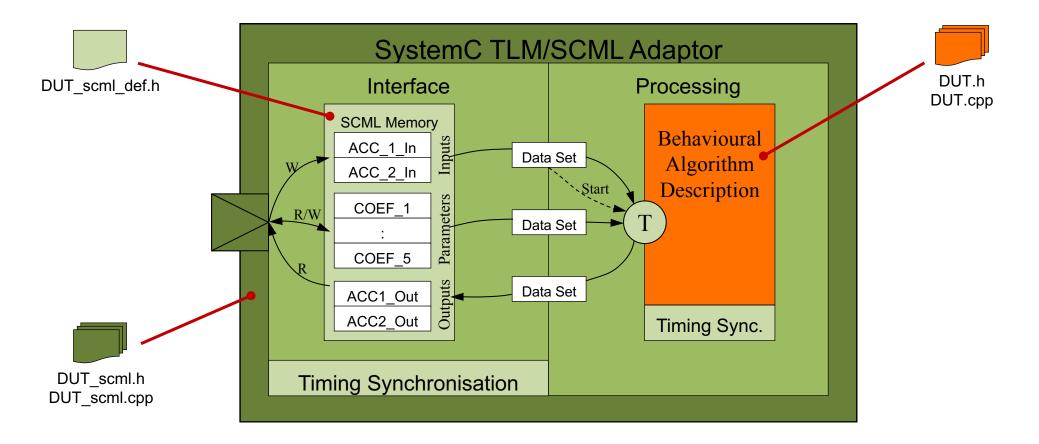

# Integration of Simulink Models into Virtual Platforms Algorithm Design & Model Generation

- ► Algorithm Design

- Mathematical representation

- Multi-domain simulation environment

- Early algorithm verification within its environment

- ► Model Generation

- ► Automatic code generation (SystemC TLM)

- ► IP-XACT register description as input

- Behavioural description integrated in SystemC TLM wrapper

- Self-testing SystemC TLM testbench

- ► IP-XACT register description as output

26 Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

# Integration of Simulink Models into Virtual Platforms Model Generation - IP-XACT Register Mapping (I/O, Parameters)

#### Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

# Integration of Simulink Models into Virtual Platforms Model Generation - SystemC TLM/SCML Adaptor Architecture

#### Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

# Integration of Simulink Models into Virtual Platforms Integration and Simulation - Manual Import of SystemC Module

| Import SystemC Modules |                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |

|------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Files Include Paths    | •                                                                        | 3     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1 |                      |

|                        | Simulink/DUT_VP/I                                                        | DUT_scml/src/DUT_scml.cpp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |

|                        | A SystemC Build Configuration                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |

| Add                    | FromSource <default></default>                                           | Setting Add                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |

| Import all modules     | — Path Environment Variables — Makefile Includes                         | A SystemC Build Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | २ <mark>×</mark>     |

| C Import modules:      | Dynamic Load Primitive Channel Payload Headers                           | FromSource <default></default>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                    |

| Generate TLM proto     | Source Files                                                             | Setting Compiler Compiler Compiler C/PROGRA~1/MATLAB/R2016a/bin/win64 *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Add<br>Remove        |

| Reset                  | Libraries<br>Template Fallback Libraries<br>Compile Flags<br>Link Flags  | Primitive Channel Payload Headers Infrastructure parameters Source Files Header Files Include Paths                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Move Up<br>Move Down |

|                        | Oynamic Library Search Paths Outline Scripts Unevaluated Parameter Files | Library Paths Library Paths Libraries Template Fallback Libraries Compile Flags Link Flags                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |

|                        | Active library set: C:/Users/maabit/PlatformCreator/worka                | Elin Flags Dynamic Library Search Paths Build Scripts Unevaluated Parameter Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |

|                        |                                                                          | Add Clone Remove Rename Make default                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | OK Cancel            |

## 2.9 Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

# Integration of Simulink Models into Virtual Platforms Integration and Simulation - SystemC Module in Synopsys<sup>®</sup> Virtualizer<sup>™</sup>

## 30 Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

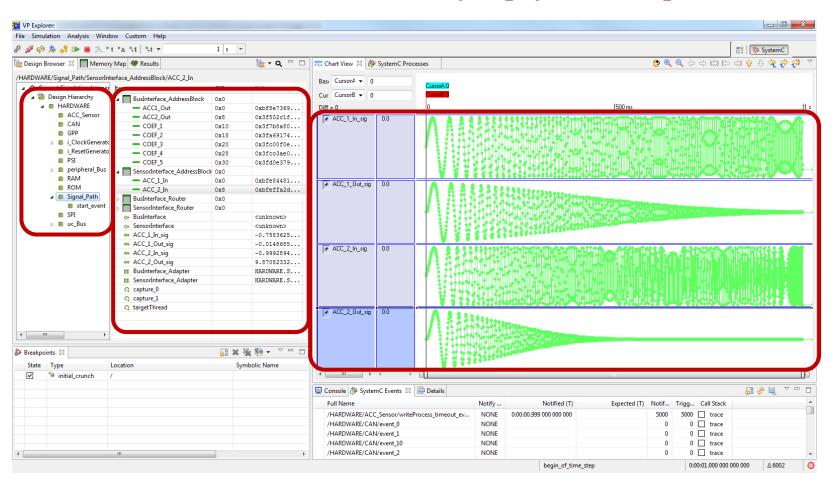

# Integration of Simulink Models into Virtual Platforms Integration and Simulation – Simulation in Synopsys<sup>®</sup> VPExplorer

## 31 Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

32 Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

# Integration of Simulink Models into Virtual Platforms Summary – Bosch Workflow

## 34 Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

# Integration of Simulink Models into Virtual Platforms Summary & Conclusion

► Developed method:

Automated integration of Simulink signal processing behaviour modules into Virtual Platforms

- ► Generated artefacts:

- ► Functional core

- SystemC TLM2.0 Wrapper with SCML registers based on IP-XACT description

- Code connecting wrapper and functional core

- ► Benefits:

- Increase of efficiency for integration signal processing behaviour into VPs

- Earlier availability of functional VPs of signal processing ASICs

- ► Inherent consistency between Simulink model and VP

Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017

© Robert Bosch GmbH 2017. All rights reserved, also regarding any disposal, exploitation, reproduction, editing, distribution, as well as in the event of applications for industrial property rights.

# Integration of Simulink Models into Virtual Platforms Trademark Attribution

- ► Accelera, SystemC and IP-XACT are trademarks of Accellera Systems Initiative Inc.

- ▶ BOSCH is a trademark of Robert Bosch GmbH.

- ▶ IEEE and IEEE 1685: IP-XACT are registered trademarks or trademarks of IEEE.

- ► Magillem is a registered trademark of Magillem S.A.

- MathWorks, MATLAB, Simulink, Stateflow, DSP System Toolbox, Simulink Coder, Embedded Coder, HDL Coder and HDL Verifier are trademarks or registered trademarks of The MathWorks Inc.

- Oracle and Java are registered trademarks of Oracle and/or its affiliates.

- Synopsys, Virtualizer, Platform Architect and VCS are trademarks or registered trademarks of Synopsys Inc.

- ► Other product or brand names may be trademarks or registered trademarks of their respective holders.

36 Automotive Electronics | Andreas Mauderer (AE/EID2), Alexander Schreiber (MathWorks) | 27.06.2017 © Robert Bosch GmbH 2017. All rights reserved, also regarding any disposal, exploitation, reproduction, editing, distribution, as well as in the event of applications for industrial property rights.

# THANK YOU