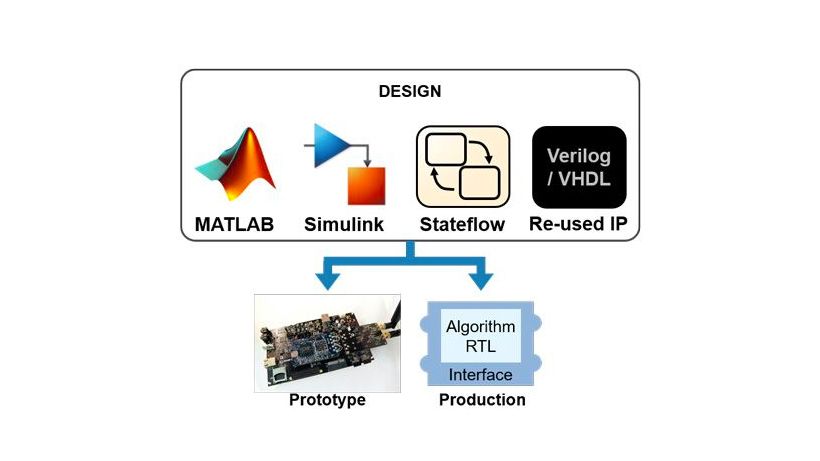

HDL Coder enables high-level design for FPGAs, SoCs, and ASICs by generating portable, synthesizable Verilog®, SystemVerilog, and VHDL® code from MATLAB functions, Simulink models, and Stateflow charts. You can use the generated HDL code for FPGA programming, ASIC prototyping, and production design.

HDL Coder includes a workflow advisor that automates prototyping generated code on AMD®, Intel®, and Microchip boards and generates IP cores for ASIC and FPGA workflows. You can optimize for speed and area, highlight critical paths, and generate resource utilization estimates before synthesis. HDL Coder provides traceability between Simulink models and generated Verilog, SystemVerilog, and VHDL code, enabling code verification for high-integrity applications adhering to DO-254 and other standards.

High-Level Hardware Design

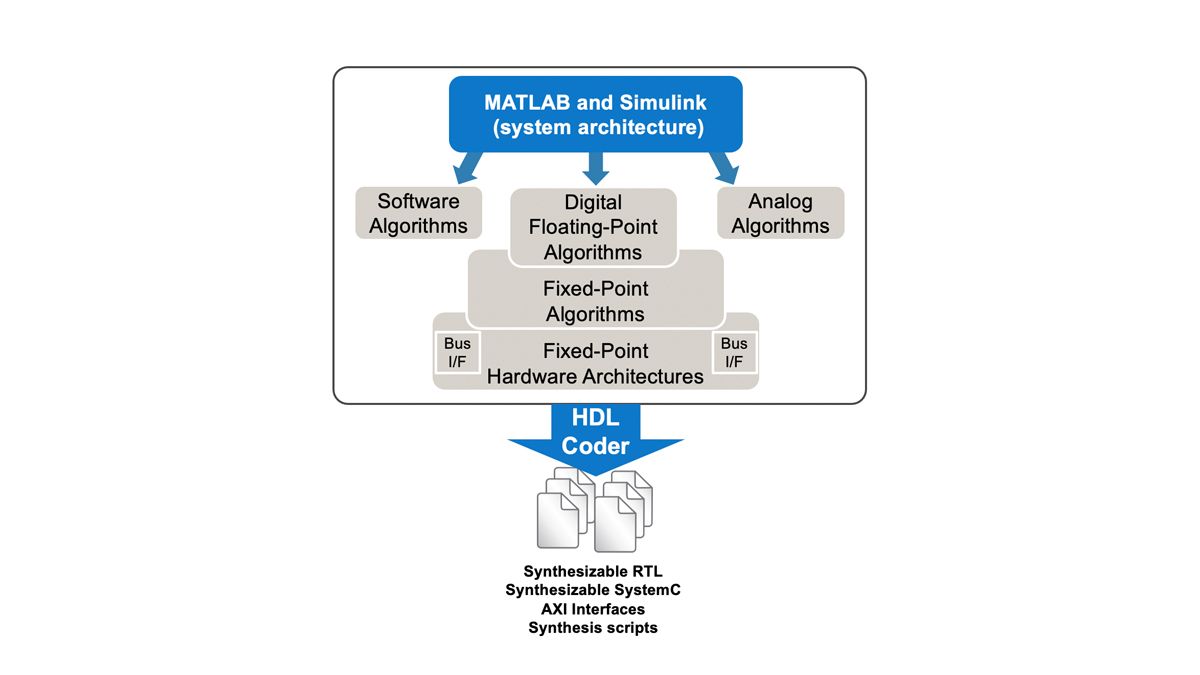

Design your subsystem by choosing from more than 300 HDL-ready Simulink blocks and MATLAB functions; add Stateflow charts, Simscape models, and deep learning networks. Simulate the hardware behavior of your design, explore alternative architectures, and generate synthesizable Verilog, SystemVerilog, or VHDL using fixed-point or floating-point data types or a combination of both.

Vendor-Independent Targeting

Generate synthesizable RTL that is target-optimized for FPGAs from leading vendors, and use it with ASICs as well. Reuse the same models for prototype and production code generation.

Design Optimization

Explore a wide variety of hardware architecture and fixed-point quantization options before committing to an RTL implementation. Use high-level synthesis optimizations such as resource sharing, pipelining, and delay balancing, that efficiently map to device resources such as logic, DSPs, and RAMs.

FPGA-Based Devices

Generate RTL that maps efficiently to AMD, Intel, and Microchip FPGA and SoC devices. Map inputs and outputs to device-level I/O and AXI registers using hardware support packages for popular boards, or define your own custom reference design.

ASIC Workflows

Design and verify your architecture and high-level hardware functionality in the context of your mixed analog, digital, and software system. Generate RTL with high quality-of-results (QoR), or generate synthesizable SystemC for use with Cadence® Stratus HLS.

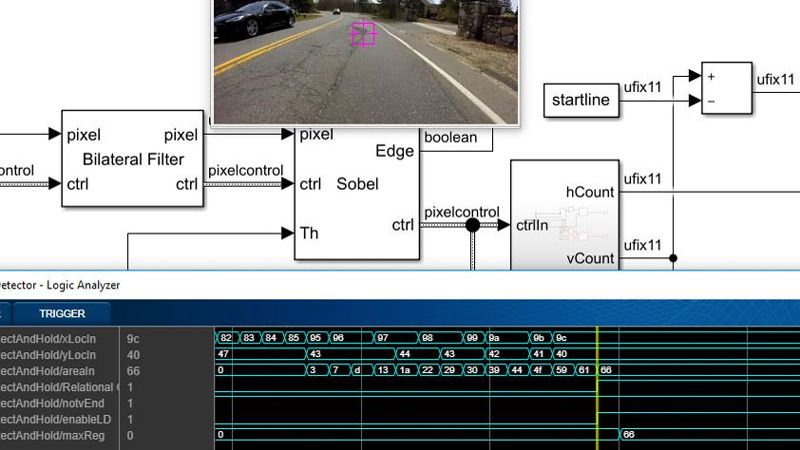

Application Development

Design communications algorithms with subsystems and blocks from Wireless HDL Toolbox, or develop streaming implementations of vision processing algorithms using Vision HDL Toolbox. Implement complex low-latency motor control systems.

Examples (Communications, Vision, Motor Control)

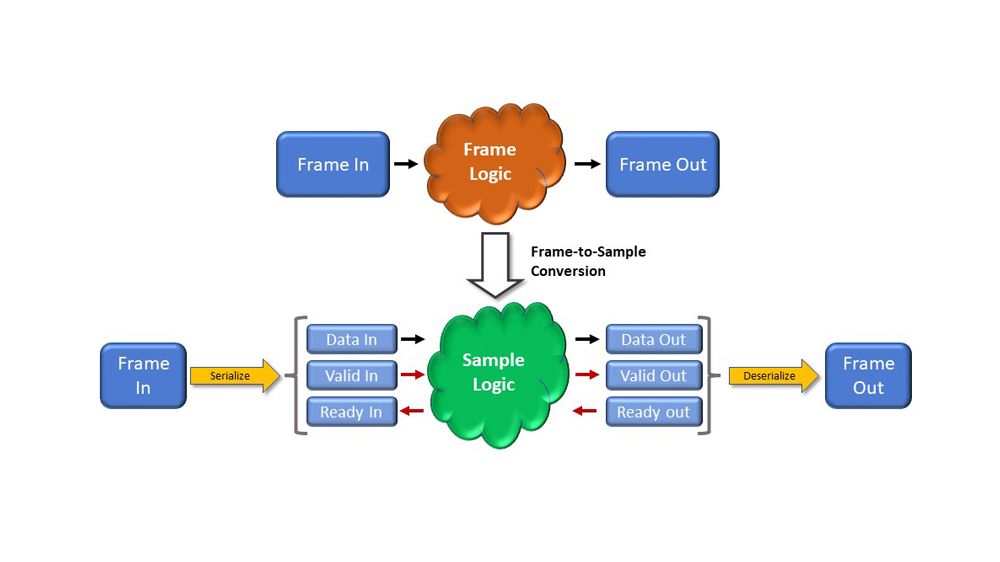

Design for Hardware

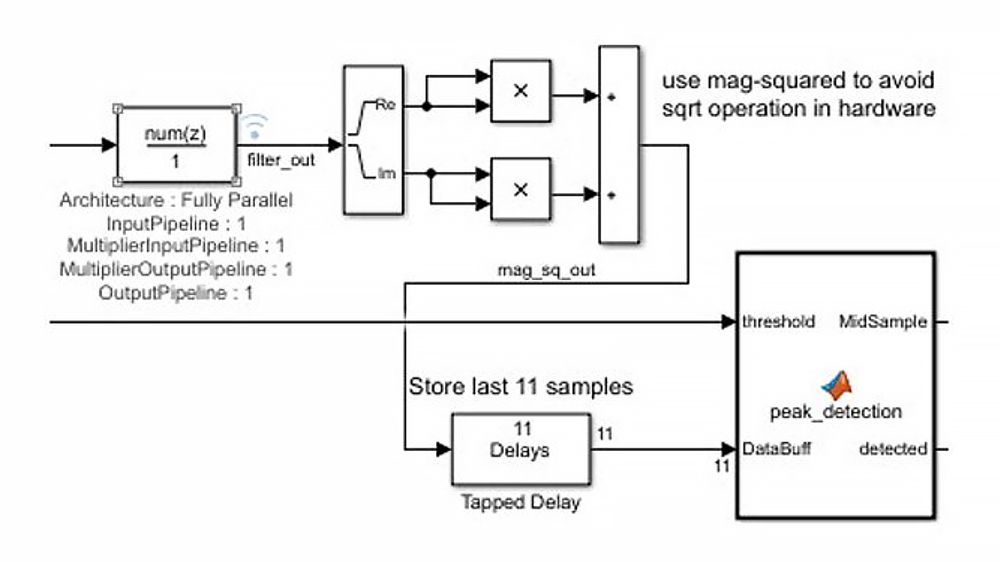

Develop algorithms that work efficiently on streaming data. Add hardware architecture details with HDL-ready Simulink blocks, custom MATLAB Function blocks, and Stateflow charts.

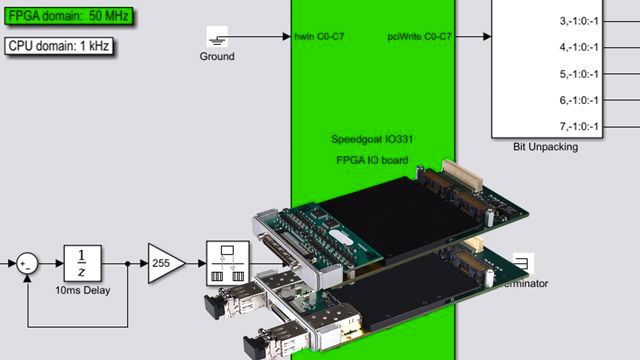

Real-Time Simulation and Testing

Target Speedgoat programmable FPGA I/O modules using the HDL Workflow Advisor, and simulate using Simulink Real-Time, or use additional FPGA I/O modules from dSPACE and NI. Generate native floating-point HDL code to simplify workflows for high-accuracy prototyping.

Early Verification

Use with HDL Verifier to ensure your generated RTL will function as required in its system context. Verify generated HDL with MATLAB and Simulink testbenches using cosimulation with leading HDL simulators. Use FPGA-in-the-loop testing to verify your design’s implementation on FPGA development boards.

Product Resources:

“Simulink helps system architects and hardware designers communicate. It is like a shared language that enables us to exchange knowledge, ideas, and designs. Simulink and HDL Coder enable us to focus on developing our algorithms and refining our design via simulation, not on checking VHDL syntax and coding rules.”

Marcel van Bakel, Philips Healthcare