# MATLAB EXPO 2019

Top Down Modeling and Analysis of Analog Mixed-Signal Systems

Rajesh R. Berigei Worldwide Semiconductor Manager, MathWorks

# Agenda

- What is Top Down Modeling and Analyis

- Why is Top Down relevant to Analog Mixed-Signal (referred to as AMS)

- Tools, Flows and Methodology to support a Top Down AMS workflow

- Using a Top Down AMS Workflow to implement

- Phased Locked Loop

- Analog to Digital Converter

- SerDes (was covered in previous talk)

📣 MathWorks<sup>.</sup>

#### What is Bottoms-up Analysis

Assemble AMS building blocks and analyze via simulation AMS building blocks: MOS, BJT, Diodes, Resistors, Capacitor, Logic Gates

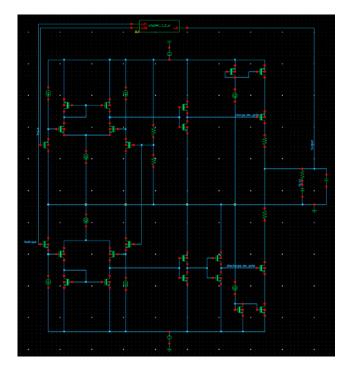

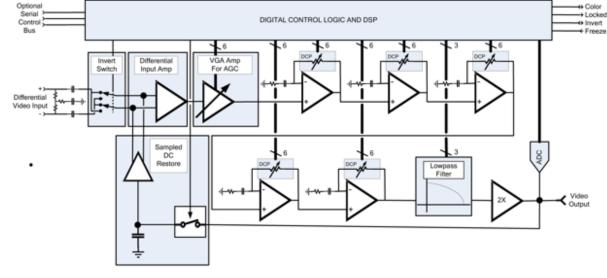

MATLAB EXPO 2019 Charge Pump Simulation Time: Seconds to Minutes Video Cable Equalizer Simulation Time: Hours to Days

MathWorks<sup>®</sup>

#### **Other Pitfalls Of Bottoms-up Analysis**

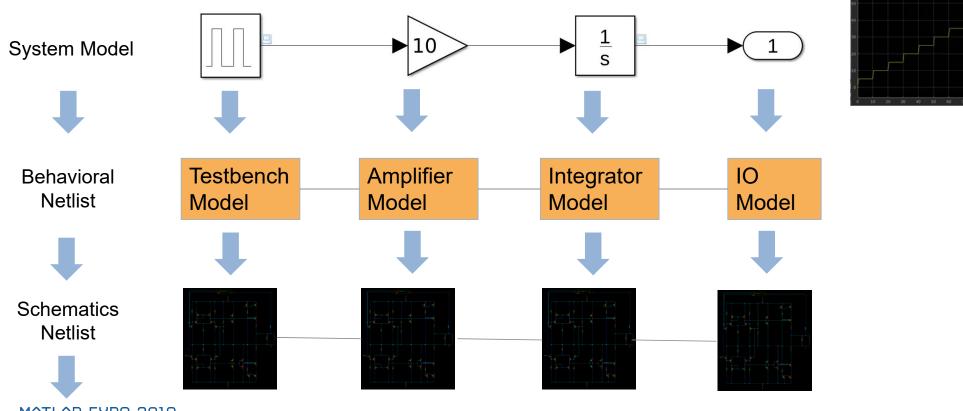

# What is Top Down Modeling and Analysis

Integrating a pulse train

MATLAB EXPO 2019 To Tapeout

#### What is Top Down Analog Mixed-Signal Design

EE Times - Top-down verification guides mixed-signal designs <u>Ken Kundert and Henry Chang.</u> <u>Partners, Designer's Guide</u> Consulting, Los Altos, CA

"In a top-down approach, the architecture of the chip is defined as a block diagram and simulated and optimized using a system simulator such as Matlab **or** Simulink. From the high-level simulation, requirements for the individual circuit blocks are derived."

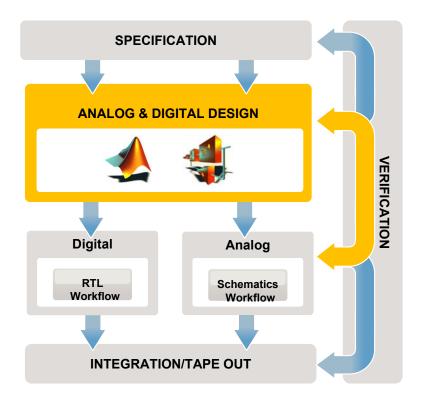

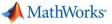

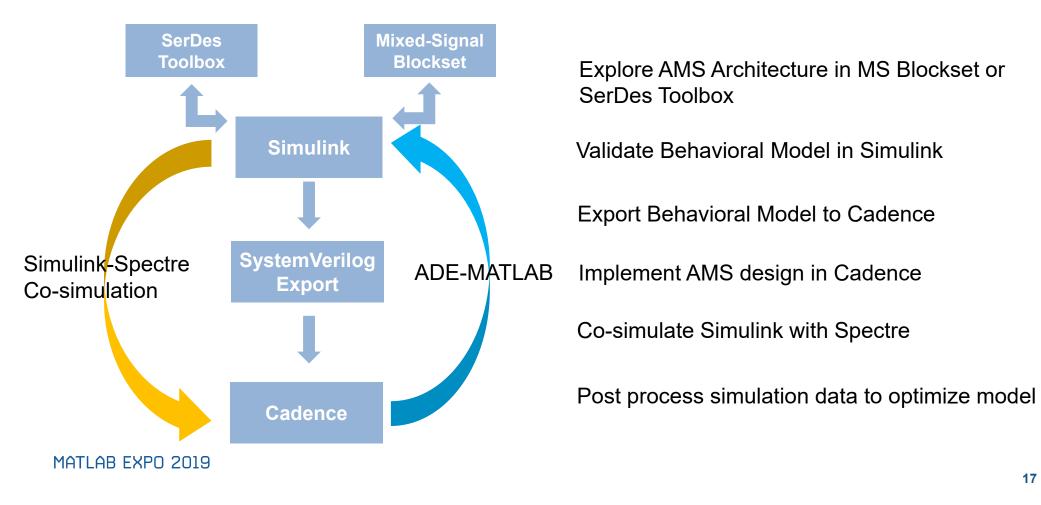

## **Usage of Tools in a Top Down AMS Framework**

📣 MathWorks

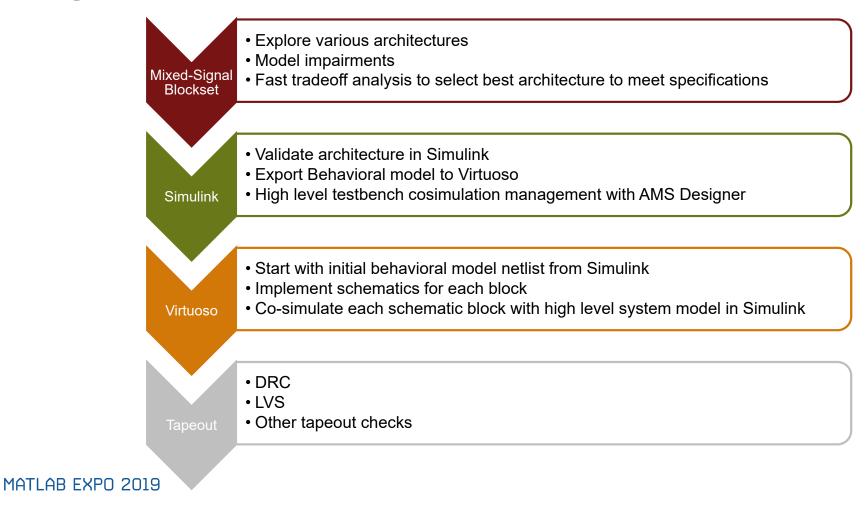

# PLL Design Architectural Selection With Mixed-Signal Blockset

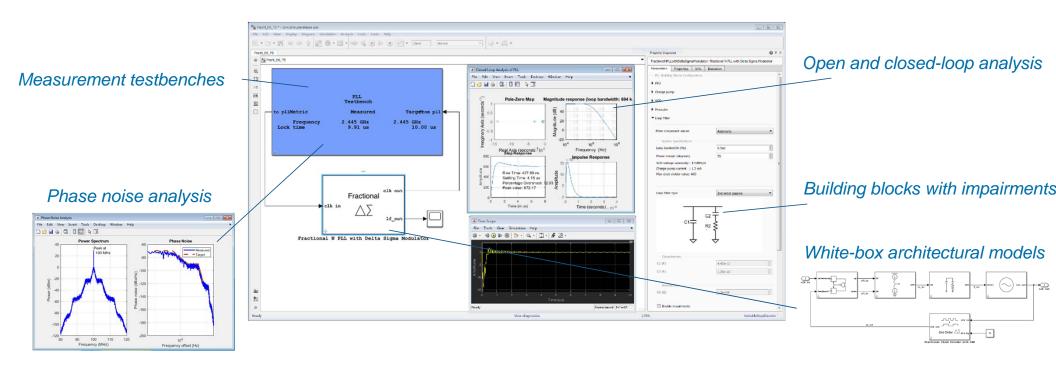

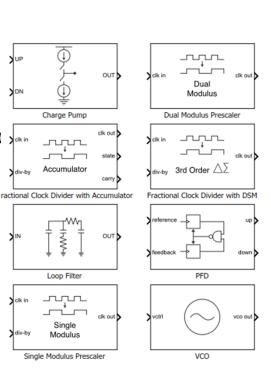

# **Explore Various PLL Architectural Models**

Model PLL and ADCs using architectural models

- Integer-N PLLs

- Fractional-N PLLs

- Flash, SAR ADCs

📣 MathWorks<sup>.</sup>

# **PLL Model Refinement –Impairments**

- Get started in your design using building blocks including impairments

- Finite rise and fall time

- Leakage, imbalance

- Phase noise

- Aperture jitter

- PLL lock time and frequent

- PLL phase noise profile

| Configura | Charge pump       | VCO      | Prescaler   |             |       |          |

|-----------|-------------------|----------|-------------|-------------|-------|----------|

|           |                   |          |             | Loop Filter | Probe | Analysis |

|           | ation             |          |             |             |       |          |

| Outpu     | it current (A)    | ср       |             |             |       | :        |

| Input     | threshold (V)     | ).5      |             |             |       | :        |

| mpairm    | ents              |          |             |             |       |          |

| Z Enable  | e impairments     |          |             |             |       |          |

|           | nt Impairments -  |          |             |             |       |          |

|           | nt imbalance (A)  | 1e-7     |             |             |       | :        |

|           | ige current (A)   | 1e-8     |             |             |       |          |

|           | lvanced           |          |             |             |       |          |

| Up        |                   |          |             |             |       |          |

| Rise      | /fall time (s)    | 50e-     | 12          |             |       | :        |

| Minim     | ium Up propagat   | ion dela | ay: 49ps    |             |       |          |

| Prop      | pagation delay (s | ) 60e-   | -12         |             |       | :        |

| Dow       | 'n                |          |             |             |       |          |

| Rise      | /fall time (s)    | 20e-     | -12         |             |       | :        |

| Minim     | ium Down propa    | gation o | delay: 32ps |             |       |          |

|           | pagation delay (s | ) 40e-   | 12          |             |       | 1        |

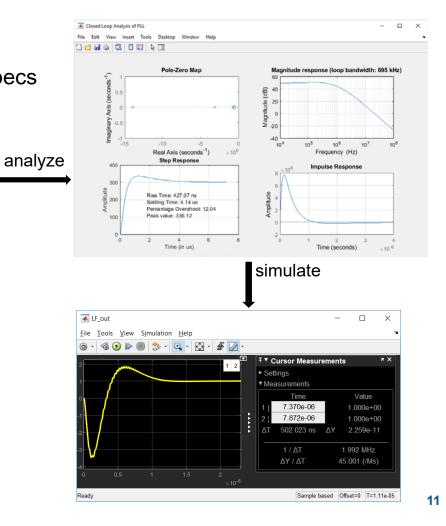

### **Configure Each PLL Component and Run**

- Model AMS behavior and impairments using your specs

- Perform open and closed-loop PLL analysis

|                    | IntegerNPLLwithSingleModulusPrescaler (mask)                                                                                                                                                                                                                                                   |                   |     |           |               |       |          |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----|-----------|---------------|-------|----------|--|--|

|                    | Frequency synthesizer with single modulus prescaler based integer N PLL architecture.<br>PLL Building Blocks Configuration                                                                                                                                                                     |                   |     |           |               |       |          |  |  |

|                    |                                                                                                                                                                                                                                                                                                |                   |     |           |               |       |          |  |  |

|                    | PFD                                                                                                                                                                                                                                                                                            | Charge pump       | VCO | Prescaler | Loop Filter   | Probe | Analysis |  |  |

| Fractional Clk out | Filter component values       Automatic <ul> <li>System Specifications</li> <li>Loop bandwidth (Hz)</li> <li>1e6</li> <li>Phase margin (degrees)</li> <li>45</li> <li>VCO voltage sensitivity : 100MHz/V</li> <li>Charge pump current : 10 mA</li> <li>Min clock divider value : 70</li> </ul> |                   |     |           |               |       |          |  |  |

| MATLAB EXPO 2019   | Loop                                                                                                                                                                                                                                                                                           | D Filter Type 3rd | 2 Ţ | R3        | <br>= c3<br>7 |       | T        |  |  |

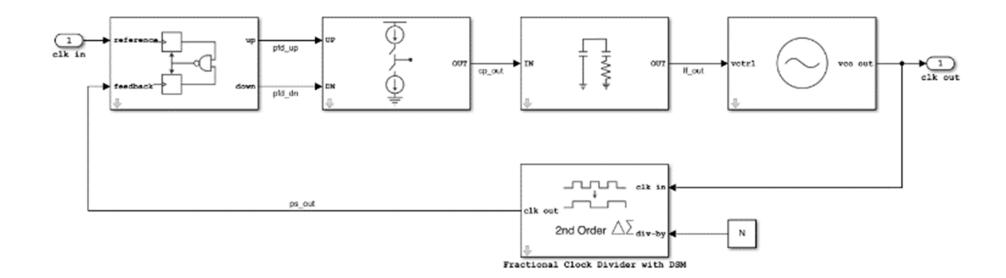

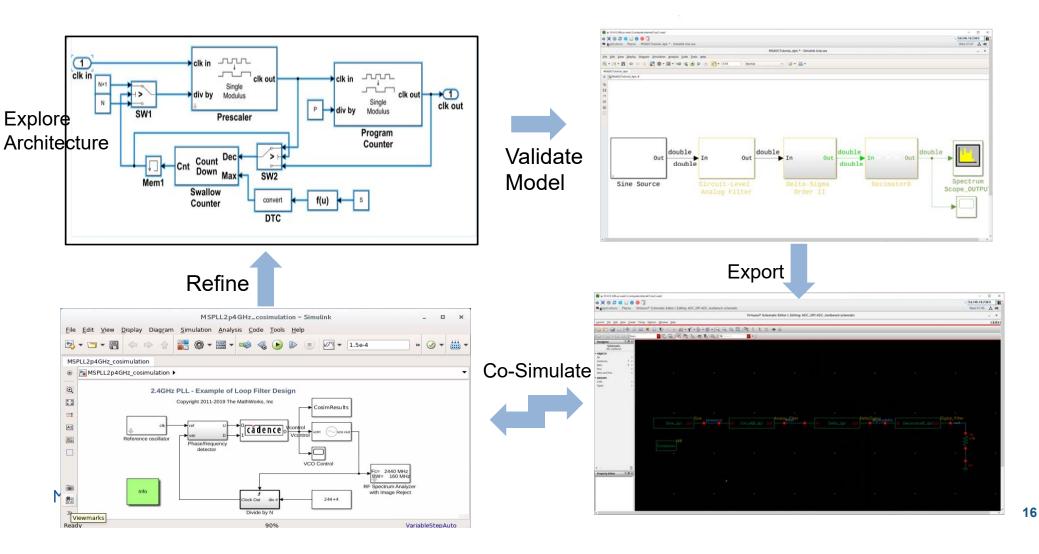

## Validate Selected Architecture in Simulink

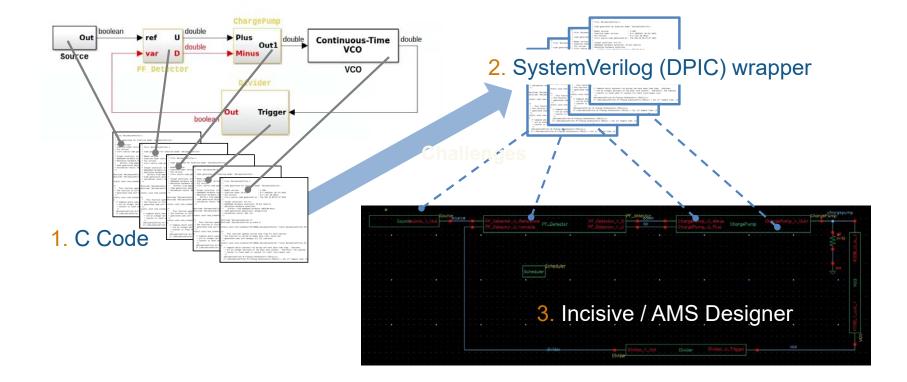

## **Export PLL Behavioral Model to AMS Designer**

📣 MathWorks<sup>.</sup>

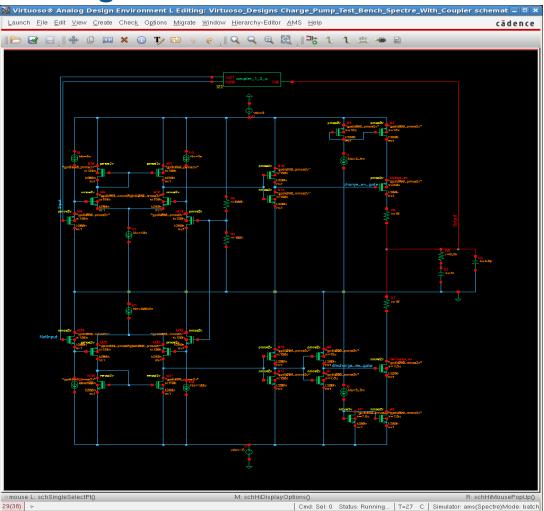

#### **Replace PLL Charge Pump With Detailed Virtuoso Schematics**

MATLAB EXPO 2019

14

# cādence

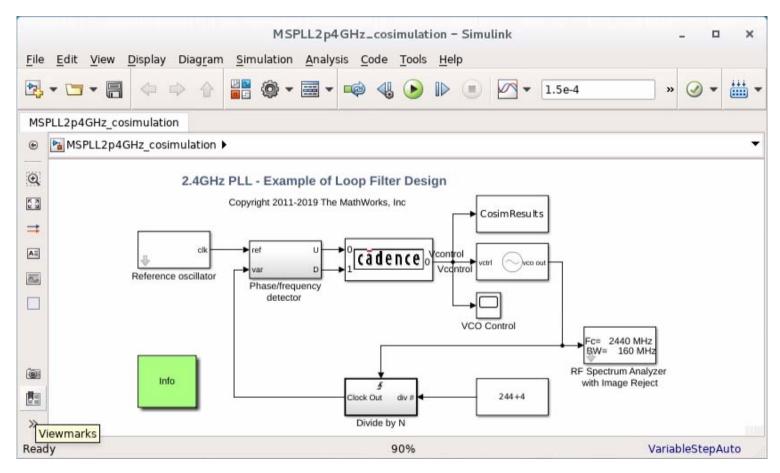

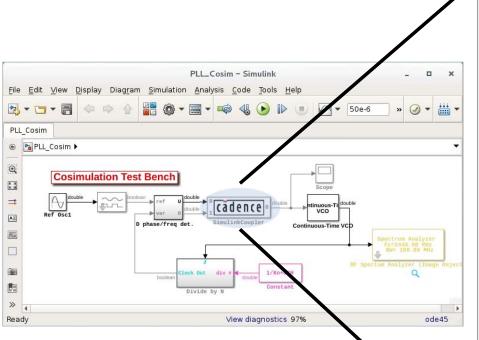

## **Co-simulate Simulink With AMS Designer**

Two variable step solvers working together Charge-pump being simulated in Spectre Rest of the PLL system simulated in Simulink

9

MathWorks<sup>®</sup>

# Similar Methodology and Tool Flow can be Applied to ADC

MathWorks<sup>®</sup>

## Summarizing Top-Down AMS Tool Flow Methodology

# **Mixed-Signal Blockset – Batteries Included!**

#### PLL

- PLL Tutorial

- · PLL Behavioral Model with Impairments

- Voltage Controlled Oscillator including Phase Noise

- PLL 2.4GHz including Cadence Virtuoso AMS Designer Analog Cosimulation

- PLL 50x including different

Measurements

- PLL with Dual Modulus Prescaler

- Fractional N PLL

#### ADC

- ADC Tutorial including Cadence Incisive Digital Cosimulation

- · ADC Behavioral Model with Impairments and Measurements

- Interleaved ADC

- Subranging ADC

- Successive Approximation ADC

- 3rd Order Sigma-Delta ADC including Circuit Level Implementation

#### Equalization

- SerDes Tutorial

- Backplane Modeling Workflow and App

- 64b/66b Coding

- 64b/67b Coding

- 8b/10b Coding

- Tunable Equalizer and Bathtub Curve Generation with Statistical Approach and Parallel Simulation

- Clock Recovery

- SerDes 10 Gbps

- · SerDes 2 Gbps with Circuit-Level CTLE

#### MATLAB EXPO 2019

#### SMPS

- Switched Mode Power Supply Tutorial

- Boost

- Buck

- Flyback

- SEPIC

www.mathworks.com/campaigns/products/offer/mixed-signal.html

# **Other Resources on AMS at MathWorks**

- Self Paced Learning

- MATLAB and Simulink for Mixed-Signal Systems

- Simulink Onramp

- MATLAB Onramp

- Available on Request

- Hands-on Analog Mixed-Signal Workshop

- Hands-on SerDes Workshop

- Seminar, presentation and demo of Analog Mixed-Signal workflows