# 高速演算を可能とするFPGAシミュレータと HDL Coder活用事例

トヨタテクニカルディベロップメント株式会社 第1計測制御事業部 シミュレーション要素開発室 高木 俊一

MathWorks Japan アプリケーションエンジニアリング部 松本 充史

### FPGAの新しいマーケットトレンド SoCデバイスのADAS用途での量産適用

### FPGAの新しいマーケットトレンド 小規模・省電力化

【レポート】

Lattice、ウェアラブル機器向けFPGAとして「iCE40 Ultra」の省電力版を発表

大原雄介 [2015/02/05]

Lattice Semiconductorは2月3日(米国時間)に、ウェアラブル機器などをターゲットにした FPGAとして「iCE40 Ultraシリーズ」の省電力版「iCE40 Ultra Lite」を発表した。

同社は昨年7月に、モバイルコンシューマ機器向けのFPGAとしてiCE40 Ultraファミリーを発表しているが、今回発表になったiCE40 Ultra Liteファミリーはその小規模・省電力版という位置づけになる。ターゲットとなるのは、従来のiCE40 Ultraファミリーがターゲットとしていた小型・省電力機器に加えて、最近急速に盛り上がりつつあるウェアラブル機器も視野に入れている(Photo01)。

### FPGAの新しいマーケットトレンド HPC(High Performance Computing)分野での応用

アルティマ、シンプレクス社と証券取引向け超低レイテンシ DMA ゲートウェイ「SimplexBLAST FPGA」を共同開発

アルティマ、シンプレクス社へBittWare(ビットウェア) 社製 FPGA 汎用ボードおよびIntilop(インティロップ)社製 Gigabit Ethernet MAC を提供、証券取引向け超低レイテンシ DMA ゲートウェイ「SimplexBLAST FPGA」を共同開発

~ 金融高頻度取引(HFT)におけるマイクロ秒単位の超低レイテンシDMA ゲートウェイを汎用FPGA ボードで 実現 ~

2014年7月15日

半導体・システム機器の輸入、販売及び技術サポートを手がける株式会社アルティマ(本社:神奈川県横浜市港北区新横浜1-5-5、代表取締役社長:三好 哲暢、以下アルティマ)は、シンプレクス株式会社(本社:東京都中央区、代表取締役社長:金子英樹、以下シンプレクス)へ、アルティマが提供する開発ソリューション、米BittWare 社 FPGA COTS (Commercial-Off-The-Shelf) ボードおよび米Intilop 社 超低レイテンシGigabit Ethemet MAC (TCP/IP Offload Engine) を提供、東京証券取引所の株式売買システム「arrowhead」(こ特化した超低レイテンシDMA ゲートウェイ「SimplexBLAST FPGA (シンプレクス・ブラスト・エフピージーエー)」を共同開発したことを発表します。

「SimplexBLAST FPGA」は、証券会社が機関投資家から受けた注文を、人手を介さずに直接取引所に取り次ぐダイレクト・マーケット・アクセス(DMA: Direct Market Access)業務をサポートする証券会社向けソリューションです。証券会社が機関投資家から受けた注文をチェックした後、取引所に取り次ぐまでの「取次処理速度」を超高速化させることで、高頻度取引(HFT:High Frequency Trading)の実現をサポートします。

### FPGAの新しいマーケットトレンド データセンターでのDeep Learningの高速処理に適用

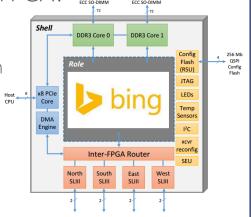

### Catapult FPGA Accelerator Card

- Altera Stratix V D5

- 172,600 ALMs, 2,014 M20Ks, 1,590 DSPs

- PCIe Gen 3 x8

- 8GB DDR3-1333

- Powered by PCIe slot

- Torus Network

### What goes on the FPGA?

- Shell handles all I/O & management tasks

- Role is only application logic

- FIFO access to Shell

- Role is Partial Reconfig boundary

"Transitioning from the Era of Multicore to the Era of Specialization" Microsoft Research https://www.sics.se/ssw2014/speakers/doug-burger

### フレキシビリティ、効率性、スケーラビリティを備えたFPGA

- 逐次処理:CPU,並列処理:FPGA,GPU,ASIC

- FPGAは高性能、スケーラビリティがあり、かつ低消費電力 ⇒高性能演算に最適なデバイス

### PERFORMANCE COMPARISON BETWEEN GPUS, ASICS AND FPGAS ON DISTRIBUTED DNN TRAINING

| Dev | rice | # Nodes | Normalized Performance $[Ops/(s*mm^2)]$ | Energy Efficiency [Ops/W] |

|-----|------|---------|-----------------------------------------|---------------------------|

|     | FPGA | 1       | 1.97G                                   | 29.5G                     |

| FPC |      | 9       | 1.92G                                   | 28.8G                     |

|     |      | 64      | 1.92G                                   | 25.1G                     |

|     |      | 1       | 1.75G                                   | 5.33G                     |

| GP  | GPU  | 9       | 874M                                    | 2.90G                     |

|     |      | 64      | 436M                                    | 1.66G                     |

| AS  | IC   | 64      | 15.7G                                   | 148G                      |

|      | フレキシビリティ | スケーラビリティ | 電力効率 |

|------|----------|----------|------|

| FPGA | ある程度良い   | GPUより良い  | 良い   |

| GPU  | 良い       | 良い       | 良くない |

| ASIC | 悪い       | 非常に良い    | 良い   |

<sup>&</sup>quot;Navigating the Design Space of Reconfigurable Neural Networks Accelerators" <a href="http://wiki.epfl.ch/edicpublic/documents/Candidacy%20exam/PR15drumond.pdf">http://wiki.epfl.ch/edicpublic/documents/Candidacy%20exam/PR15drumond.pdf</a>

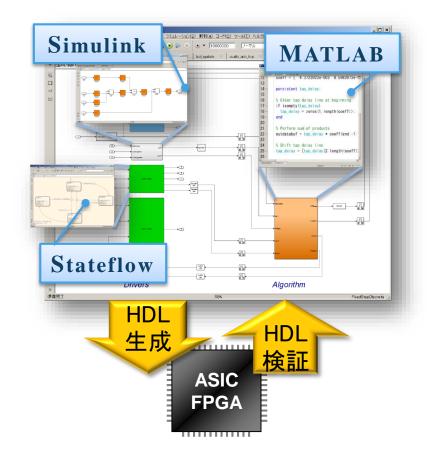

### HDL Coder<sup>™</sup>/HDL Verifier<sup>™</sup>製品概要

#### HDL Coder

- Simulink/Stateflow/MATLABから HDLコード生成

- コーディング規約準拠、可読性高い、 ターゲット依存しないVHDL/Verilog生成

#### HDL Verifier

- HDLシミュレータと連携してHDLコード検証

- FPGAボードと連携してFPGA実機検証

- DPI-Cテストベンチ生成

- System C TLMラッパー生成

# 高速演算を可能とするFPGAシミュレータと HDL Coder活用事例

2015年10月16日

トヨタテクニカルディベロップメント(株)

Toyota Technical Development Corporation

第1計測制御事業部 シミュレーション要素開発室 高木 俊一

## Agenda

- 1. TTDC会社紹介

- 2. モータシミュレータ(HILS)でFPGA採用の背景

- 3. HDL Coder活用の狙い

- 4. HDL Coder性能調査

- 5. HDL Coder活用への取り組み

- 6. まとめ

### Agenda

- 1. TTDC会社紹介

- 2. モータシミュレータ(HILS)でFPGA採用の背景

- 3. HDL Coder活用の狙い

- 4. HDL Coder性能調査

- 5. HDL Coder活用への取り組み

- 6. まとめ

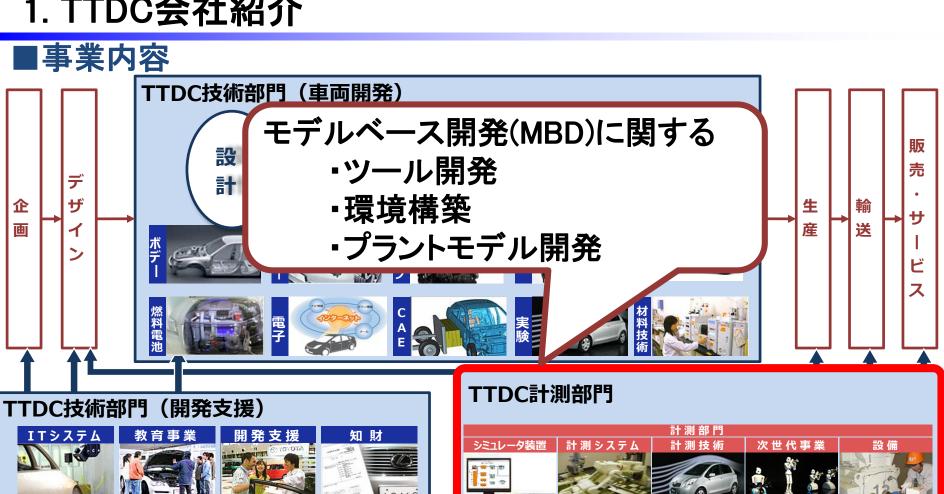

### 1. TTDC会社紹介

### トヨタテクニカルディベロップメント株式会社 (TTDC)

英文名: Toyota Technical Development Corporation

本 社: 愛知県豊田市花本町井前1-21

資 本 金 : 5.5億円 ※トヨタ自動車100%出資

設 立 : 2006年4月1日

従業員数: 5,938名(2015年4月1日現在)

売上高: 689億円(2014年度)

### 1. TTDC会社紹介

### Agenda

- 1. TTDC会社紹介

- 2. モータシミュレータ(HILS)でFPGA採用の背景

- 3. HDL Coder活用の狙い

- 4. HDL Coder性能調査

- 5. HDL Coder活用への取り組み

- 6. まとめ

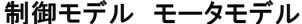

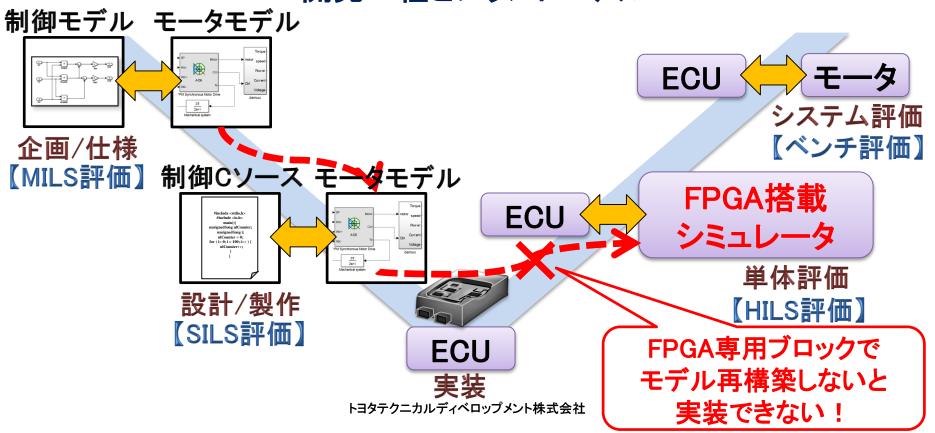

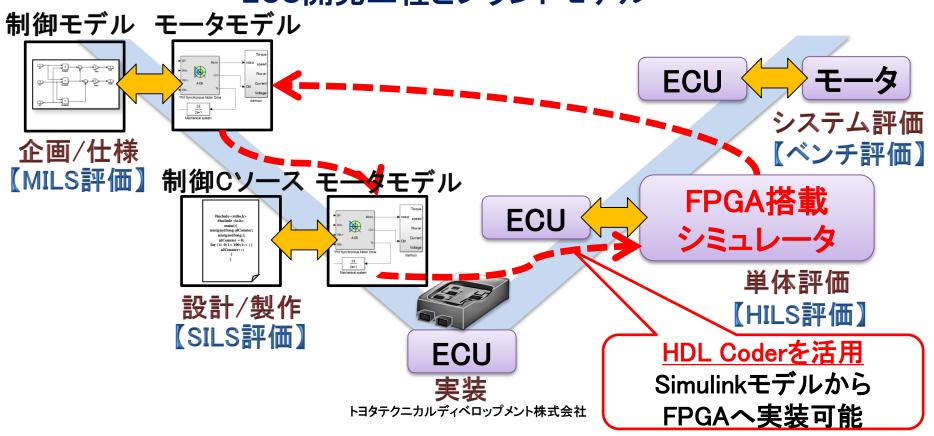

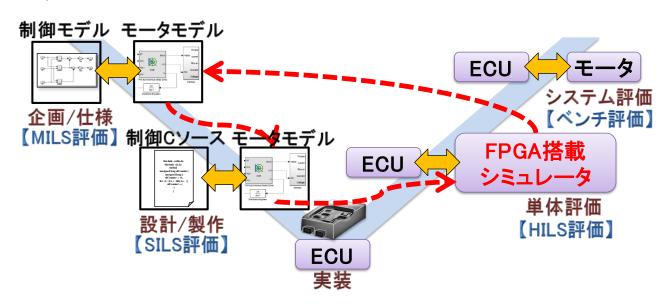

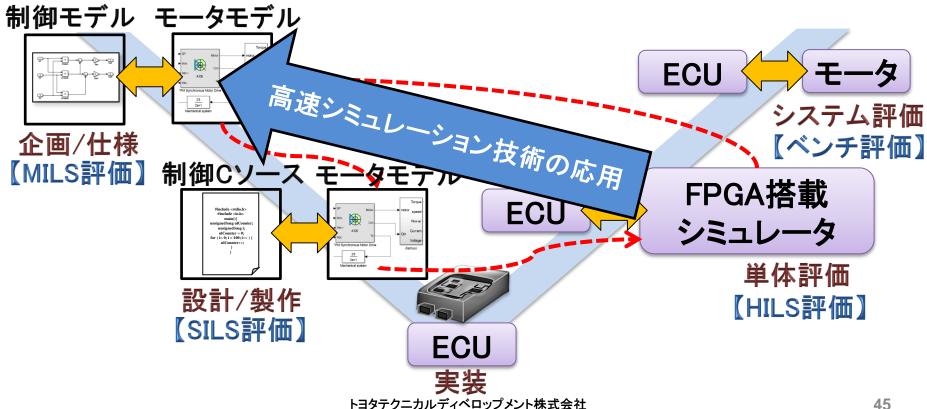

### ECU(Electronic Control Unit)のMBDにおけるVプロセス

(モータ制御開発の一例)

**ECU**

#### MILSとは

(Model In the Loop Simulation) ECU,プラントが無い状態で、システムの先行検討を可能にする手法

### 企画/仕様

【MILS評価】制御Cソース モータモデル

ECU

モータ シミュレータ

単体評価

【HILS評価】

#### SILSとは

(Software In the Loop Simulation) ECU,プラントが無い状態で、ソフトウェア評価を可能にする手法

【SILS評価】

実装

トヨタテクニカルディベロップメント株式会社

**ECU**

#### HILSとは

(Hardware In the Loop Simulation) ユニット・試験車の無い状態での 上記評価を可能にする手法

14

システム評価

【ベンチ評価】

### Vプロセスにおける仮想化範囲

仮想部分が多い

実車に近い

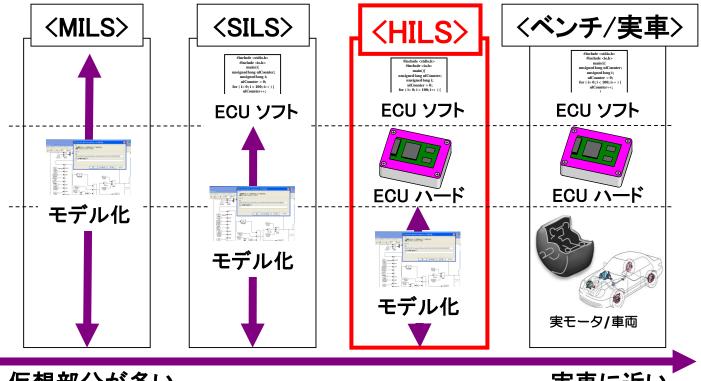

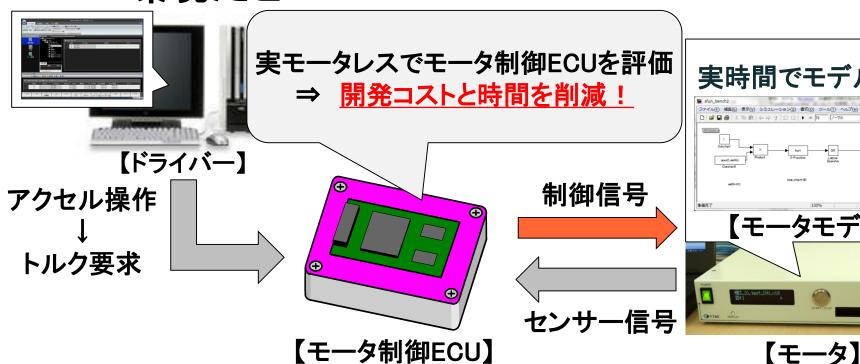

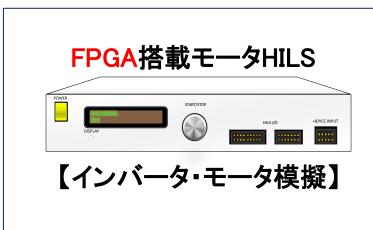

# HILS とは

- HILS=Hardware In the Loop Simulation 実ECU(Electronic Control Unit)を使用するシミュレーション手法

- ECUの制御対象をモデル(計算式)化、 専用シミュレータでリアルタイムに実行

# 実ECUを仮想環境に接続して試験/評価

# HV車のモータ制御のイメージ

# HILS環境だと・・・

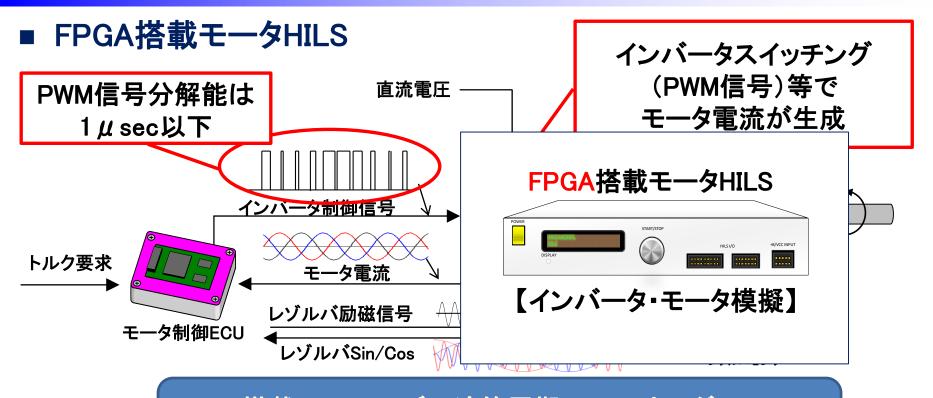

CPU搭載HILSのモデル演算周期: μ secオーダー FPGA搭載HILSのモデル演算周期: nsecオーダー

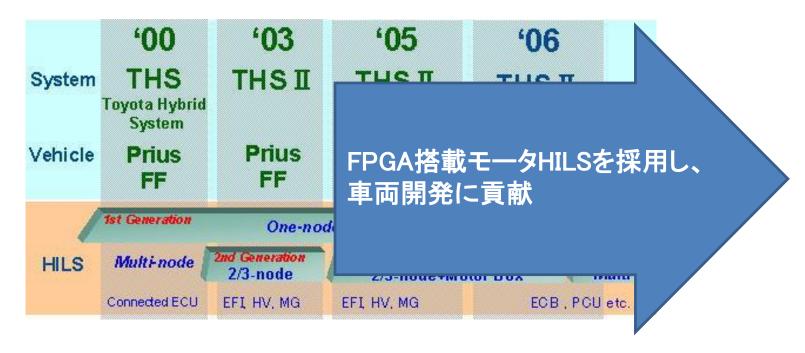

■ FPGA搭載モータHILSを用いた車両開発実績(過去事例)

出典:「2007 SAE International」Paper#2007-01-3469

## Agenda

- 1. TTDC会社紹介

- 2. モータシミュレータ(HILS)でFPGA採用の背景

- 3. HDL Coder活用の狙い

- 4. HDL Coder性能調査

- 5. HDL Coder活用への取り組み

- 6. まとめ

### ECU開発工程とプラントモデル

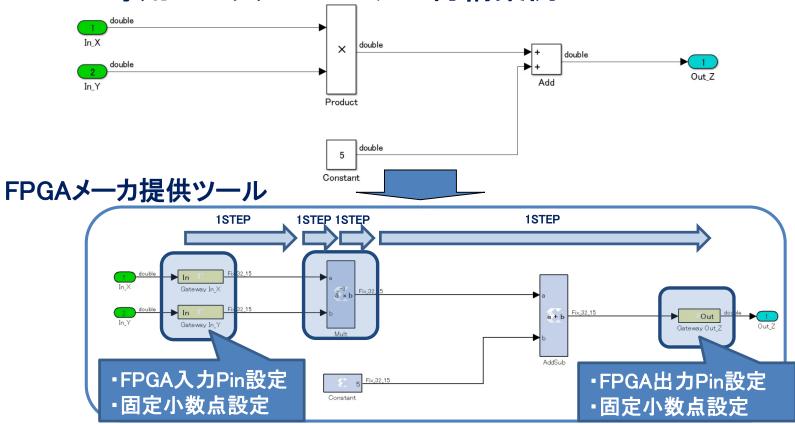

■ FPGA専用ブロックでのモデル再構築例

### ECU開発工程とプラントモデル

■ FPGA専用ブロックでのモデル再構築例

### Agenda

- 1. TTDC会社紹介

- 2. モータシミュレータ(HILS)でFPGA採用の背景

- 3. HDL Coder活用の狙い

- 4. HDL Coder性能調査

- 5. HDL Coder活用への取り組み

- 6. まとめ

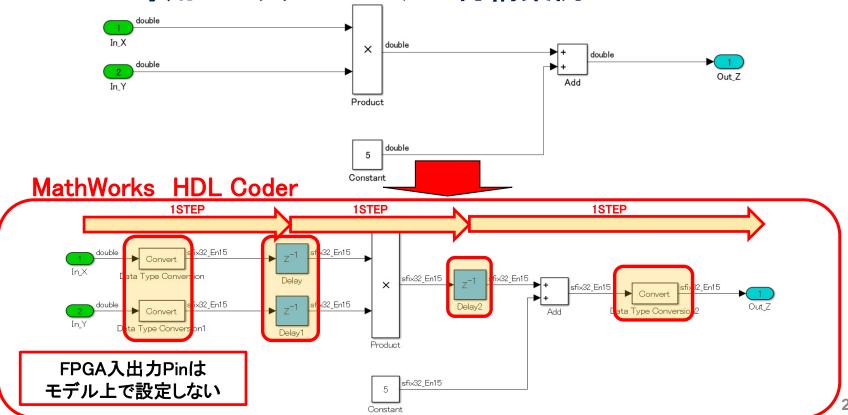

### ■ FPGAメーカ提供ツールとの比較

Simulinkモータモデルから、FPGA実装モデルを2種類作成し比較調査

- FPGAメーカ提供ツール (FPGA専用ブロック)

- MathWorks社のHDL Coder

#### モデル開発環境

| メーカー      | ソフトウェア               | Version           |

|-----------|----------------------|-------------------|

|           | MATLAB               | 7.11.0(R2010bSP1) |

|           | Simulink             | 7.6.1(R2010bSP1)  |

| MathWorks | Simulink HDL Coder   | 2.0(R2010bSP1)    |

|           | Fixed-Point Toolbox  | 3.2(R2010bSP1)    |

|           | Simulink Fixed Point | 6.4(R2010bSP1)    |

|           | FPGAメーカ提供ツール         |                   |

| FPGAメーカ   | (専用ブロックセット)          | _                 |

|           | FPGAメーカ製コンパイラ        | _                 |

### ■ HDL Coder と FPGAメーカ提供ツールの比較結果

| No | 比較項目                           | HDL Coder優劣 |  |

|----|--------------------------------|-------------|--|

| 1  | SimulinkモデルからFPGA実装までのモデル作成作業量 | 0           |  |

| 2  | Simulink環境でのモデル実行時間(モデルのデバッグ)  | 0           |  |

| 3  | HDLコードの生成時間                    | 0           |  |

| 4  | HDLコードからFPGA実装ファイル生成作業         | ×           |  |

| 5  | 実装可能なFPGA種類                    | 0           |  |

| 6  | Simulink CoderでのCコード生成対応       | 0           |  |

| 7  | FPGA実装モデルのトータル演算周期             | 0           |  |

| 8  | FPGA内の使用リソース調整                 | _           |  |

| 9  | ツール価格                          | ×           |  |

| 1 | SimulinkモデルからFPGA実装までのモデル作成作業量 | 0 |

|---|--------------------------------|---|

| 2 | Simulink環境でのモデル実行時間(モデルのデバッグ)  | 0 |

•ベースのSimulinkモデル流用により、作業時間短縮

FPGAメーカ提供ツールでは100H程度 ⇒ HDL Coderならば60H程度

・<u>ラピッドアクセラレータが使用でき、デバッグ時間短縮</u>

1secのシミュレーション時間比較

FPGAメーカ提供ツール: 70min

HDL Coder : 17min

モデル作成時間に加えデバッグ作業時間も短縮 MILS/SILSプラントモデルの流用度Up!

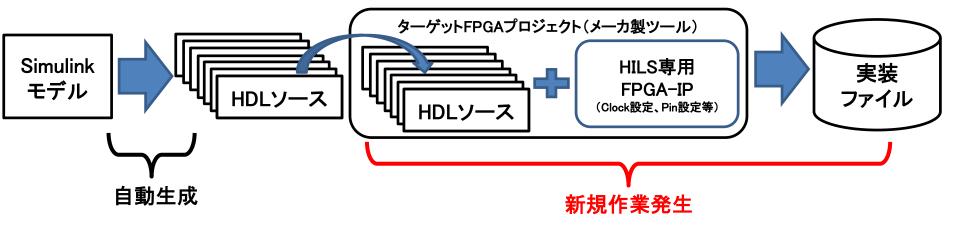

4 HDLコードからFPGA実装ファイル生成作業 ×

HDL CoderはSimulinkモデル → HDL生成までは可能だが、 ターゲットFPGA向けコンパイルは不可能(FPGA-Pin設定等)

- ▼モデル作成作業量は削減されたが、FPGA実装ファイル生成作業が新規で発生

- ⇒ FPGA実装ファイルの自動化生成ツールの開発

8 FPGA内の使用リソース調整

-

FPGAメーカ提供ツール:ターゲットFPGA専用

⇒ 最適化されたコード生成

HDL Coder

:FPGAメーカに依存しない

⇒ 汎用的なコード生成

同じ演算内容のモデルでも、生成されるコードが異なる為 FPGAに実装した際に使用するリソースにも違いが出る

8 FPGA内の使用リソース調整

\_

### FPGAリソース使用状況の比較

| No | Resource                    | FPGAメーカ提供   | ツール | HDL Code     | r   |

|----|-----------------------------|-------------|-----|--------------|-----|

| 1  | DCM_ADVs (デジタルクロックマネジャ)     | 4/12        | 33% | 4/12         | 33% |

| 2  | DSP48s (乗算器)                | 15/160      | 9%  | 75/160       | 46% |

| 3  | External IOBs (FPGAの入出力PIN) | 364/768     | 47% | 374/768      | 48% |

| 4  | RAMB16s (RAM)               | 136 / 376   | 36% | 136/376      | 36% |

| 5  | Slices (スライス)               | 18690/42176 | 44% | 16518 /42176 | 39% |

HDLコード生成時に演算ブロックの扱いが異なる

FPGAメーカ提供ツール:最適化により適したリソースへ割り当て

モデルの作り方を間違えると

- ・リソース無駄使い発生

- ・処理負荷の高い演算は実装困難

- ⇒ バランスを意識した独自ブロック(ライブラリ)の開発

### Agenda

- 1. TTDC会社紹介

- 2. モータシミュレータ(HILS)でFPGA採用の背景

- 3. HDL Coder活用の狙い

- 4. HDL Coder性能調査

- 5. HDL Coder活用への取り組み

- 6. まとめ

### 5.HDL Coder活用への取り組み

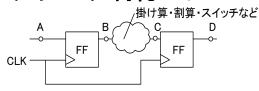

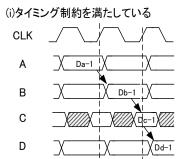

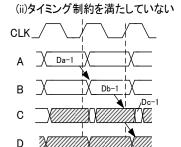

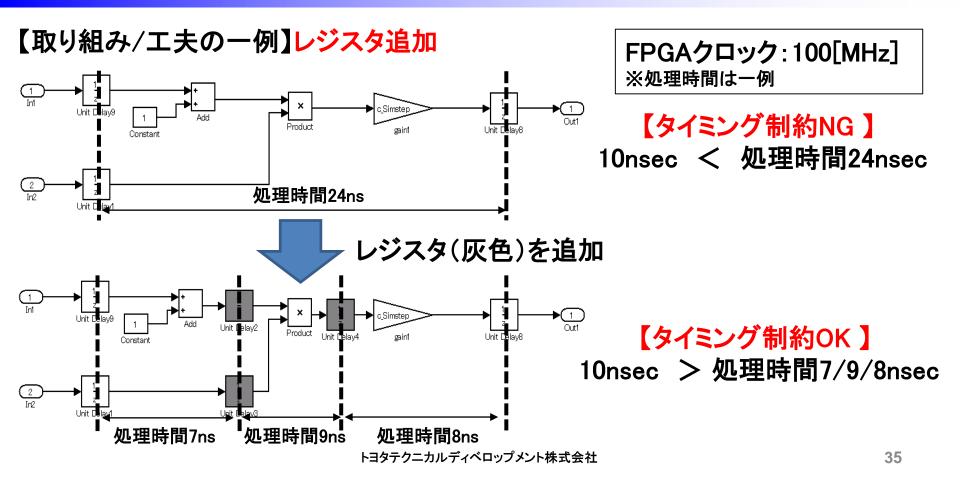

### 【課題】100[MHz]高速演算FPGAへSimulinkモデルを実装

- ⇒タイミング制約を満たすモデル設計技術が必要

- ⇒タイミング制約満たせない場合、FPGA内の演算値が不定となる。

結果として、モータシミュレーションが破綻する可能性がある。

### タイミング制約とは・・・

タイミングエラ一解消するには・・・

意図した結果が得られない トヨタテクニカルディベロップメント株式会社

## 5.HDL Coder活用への取り組み

### 5.HDL Coder活用への取り組み

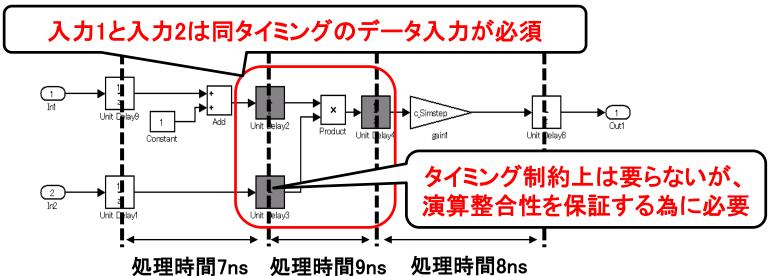

### 【技術的なPoint】同期設計

- ・レジスタ追加手法では同期性の考慮が必要

- ⇒FPGAで演算させる場合、回路が並列で動作する為

- 2入力以上のブロックに対しては同期を考慮したモデル設計が必要

トヨタテクニカルディベロップメント株式会社

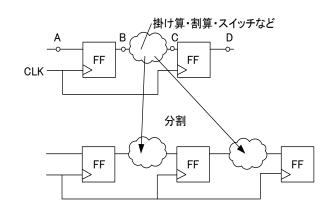

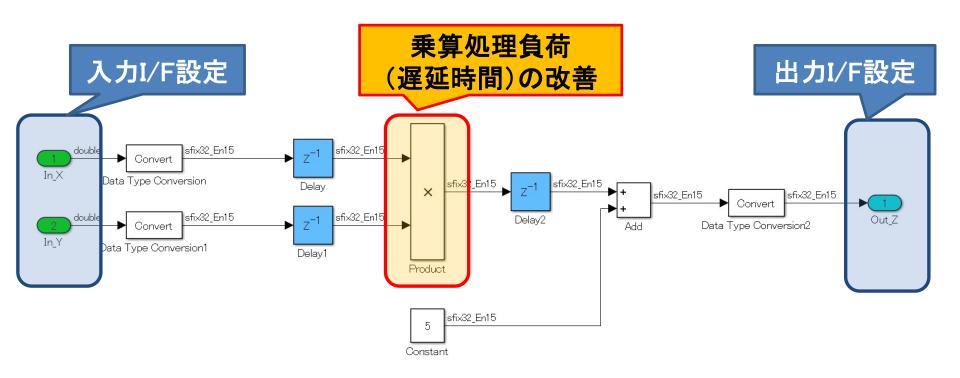

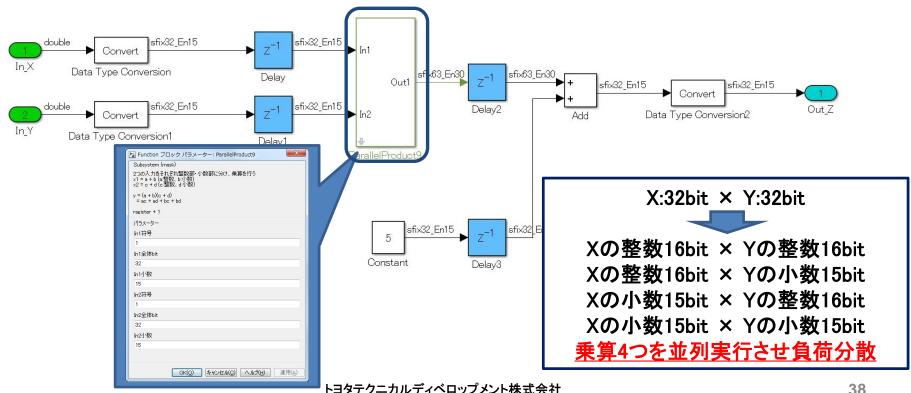

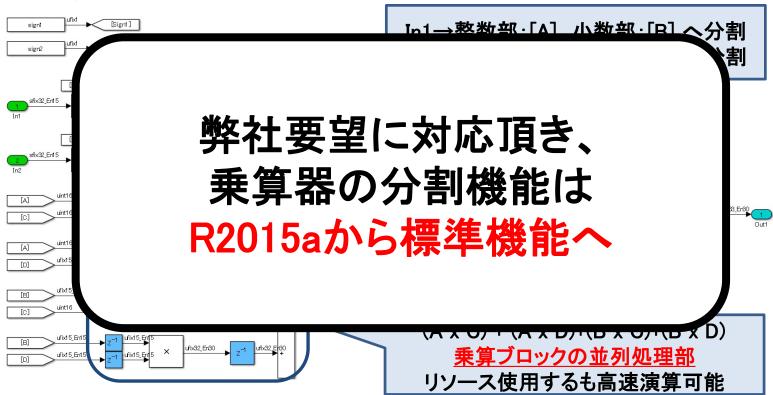

### 【取り組み/工夫の一例】独自ブロック(ライブラリ)の開発

乗算処理負荷(遅延時間)の改善

38

■ 独自乗算ブロックの中身

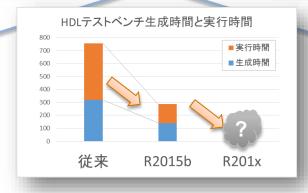

■ シミュレータ実装後のトータル演算周期(演算STEP)の短縮

従来モデル

800ns

独自取組後のモデル

600ns

### Agenda

- 1. TTDC会社紹介

- 2. モータシミュレータ(HILS)でFPGA採用の背景

- 3. HDL Coder活用の狙い

- 4. HDL Coder性能調査

- 5. HDL Coder活用への取り組み

- 6. まとめ

### 【HDL Coder活用の狙い】

Vプロセスにおいて、上流工程から下流工程まで一貫したプラントモデルで制御(ECU)評価したい

⇒ FPGA実装モデルへHDL Coderを活用

### 【 HDL Coder活用に向けた取り組みの結果】

- モデルの開発+デバッグ工程が短縮 MILS/SILSプラントモデルの流用性向上

- トータル演算周期(演算STEP数)が短縮 HILSシステムとして演算応答性が向上

- 汎用性/自由度が高い分、ノウハウも必要 リリース当初の標準機能では不十分であったが、 VerUp毎に機能改善/追加がされている

弊社のモータHILS"MotorBox3"は、 モデル開発環境としてHDL Coderを採用!

FPGAのベースクロック 100MHz( = モデル演算Step) FPGAリソースと ベースクロックを考慮した モデリング技術

Simulinkモデルから FPGA実装ファイル 自動生成ツールの開発

その他FPGA関連業務でも モデルの流用が可能になり効率化実現!

### ECU開発工程とプラントモデル

# 今後のHDL Coder VerUp.にさらなる期待!

### 高度な演算におけるキーファクター: アルゴリズム

#### 入力

- LIDAR, Radar

- 画像

- 電波

- モータの回転

- 文字入力

#### アルゴリズム

- 信号処理

- 画像認識

- 通信

- 制御

- 機械学習

#### レスポンス

- 距離・位置

- ステアリング

- 音声

- 速度

- 文字出力

高度なシステムを実現するキーファクターは 「*アルゴリズム*」

# 一般的なFPGAによるアルゴリズムの実現方法

レジスタと組み合わせロジック 記述が煩雑、行数多い 複雑な演算記述は困難

ハードウェアを意識した動作記述 スケジューリングや回路アーキテクャ を推論するためのpragma

FPGA 設計 ハードウェアを意識したブロック線図 豊富なアルゴリズムと機能ライブラリ 検証のための各種機能

- 各種解析、固定小数点化、カバレッジ

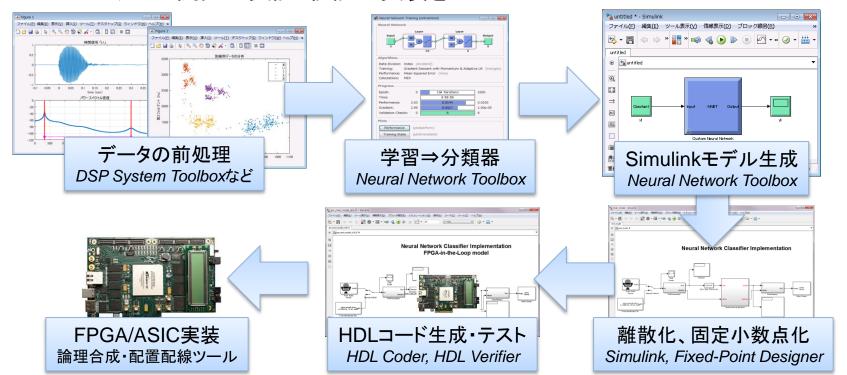

# アルゴリズムから実装までのフロー 例: Neural NetworkのFPGA実装

アルゴリズム開発~実証・検証~実装をカバーしたツールチェーン

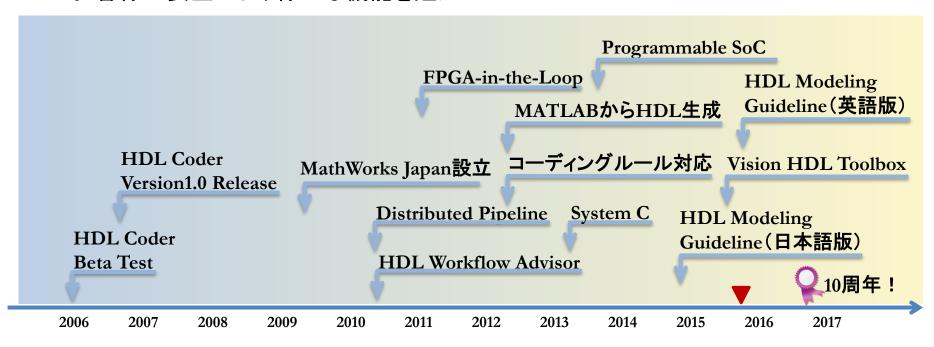

# HDLプロダクト推移

■ お客様の要望により様々な機能を追加

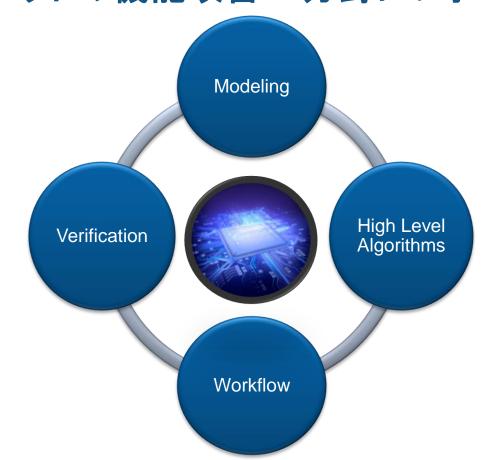

# Modeling Verification High Level Algorithms Workflow

# HDLプロダクトの機能改善:4分野にフォーカス

### **♦** MathWorks<sup>®</sup>

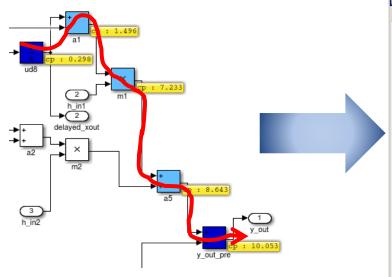

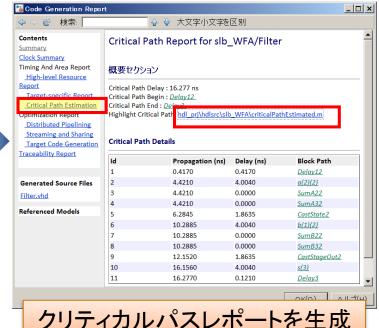

## Workflow: クリティカルパス推定

R2015a

- Modeling

Verification

High Level Algorithms

Workflow

- 論理合成を行わずに短時間でクリティカルパスを推定 ⇒タイミング解析時間の短縮

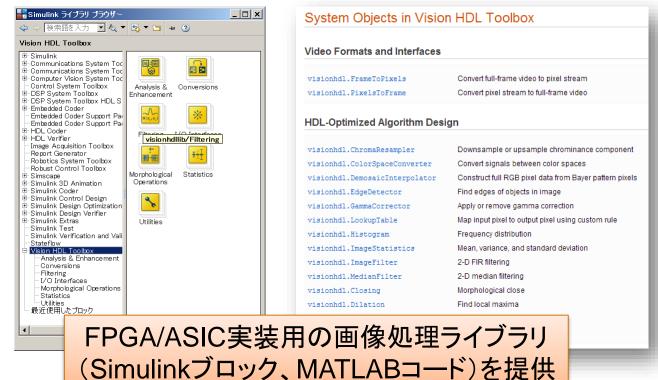

### **High Level Algorithm:**

### 画像処理ライブラリVision HDL Toolboxリリース

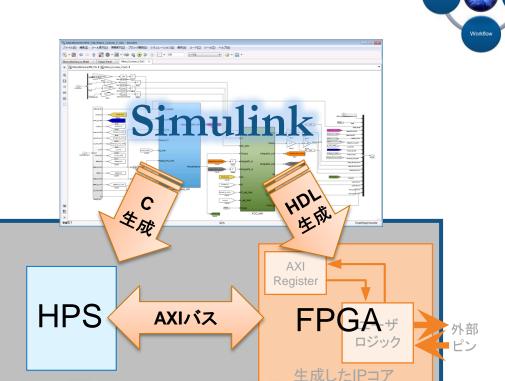

# Modeling: Programmable SoC対応

■ R2013b : Zynqサポート

■ R2014b: Altera SoCサポート

■ R2015a: AXI4-Streamサポート

R2015b:ベクターポートのAXI4-Streamサポート

Programmable SoC

### Workflow:ハードウェアサポートパッケージ

- アドオンをダウンロードして追加インストール

- FPGA/SoCボード定義ファイル、例題モデル

- 最適化ARM Cortex-M/A向けCコードライブラリ

- 各種分野向けボードをサポート

信号処理/無線通信

モータ制御

画像処理

# Verification: テストベンチの多様化とパフォーマンス向上

FPGA-in-the-Loop対応ボードと 対応インターフェース追加

チューナブルなDPI-C テストベンチ生成

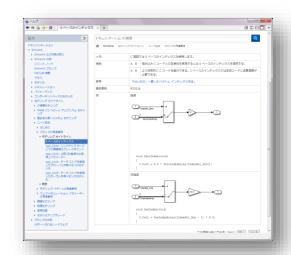

# Modeling: モデリングガイドライン

個角美質認識様は 下着く予認に、複数を整理機能を示す。特点型形の音光系形と、ては、音響線を必要に扱わった分類 下着く予認に、複数を影響を発展を対象を表現し、自然機能とはあって、事業が必要が必要が必要 の、意思性機能を必要をは、実施制度を指すがそれたが考え、力・自然を表現して、のかを機能 には、この 例に含またも効果素、行 学が使用できる場合が多り、最適情報をデバイスを含えなっていること で概要する。

# Ventication High Level Algorithms Workflow

### HDLコード生成用モデリング Verw

- HDL Modeling Guidelineを2014年 12月日本先行リリース

- 英語版を2015年8月リリース

- ユーザに配布(ヘルプドキュメント 掲載までの暫定措置)

### Cコード生成用モデリング

- Simulinkヘルプドキュメント

- JMAABガイドライン(制御向け)

## まとめ

- FPGAのマーケットトレンドの変化

- 量産適用、高性能演算への適用分野の広がり

- FPGAシミュレータ開発事例

- ECU開発用の仮想プラント(モータ)への適用

- HDLプロダクトの最新動向

- Modeling, High Level Algorithm, Workflow, Verification

### HDL Coder/HDL Verifierに関して詳しく知りたい方は・・・

FPGA/ASIC実装ビデオシリーズ

jp.mathworks.com ⇒ 製品

⇒ HDL Coder ⇒ 関連ビデオ

<a href="http://jp.mathworks.com/videos/series/fpgaasic-implementation-102284.html">http://jp.mathworks.com/videos/series/fpgaasic-implementation-102284.html</a>

© 2015 The MathWorks, Inc. MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See <a href="https://www.mathworks.com/trademarks">www.mathworks.com/trademarks</a> for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.