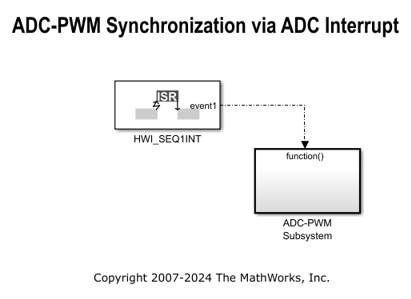

C28x Hardware Interrupt

Interrupt Service Routine to handle hardware interrupt on C28x processors

Libraries:

C2000 Microcontroller Blockset /

Scheduling

Description

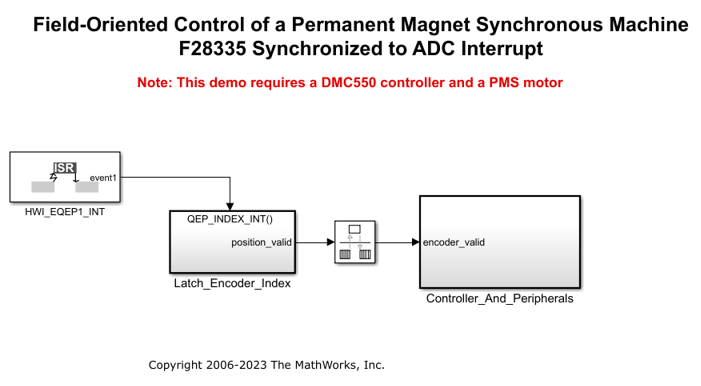

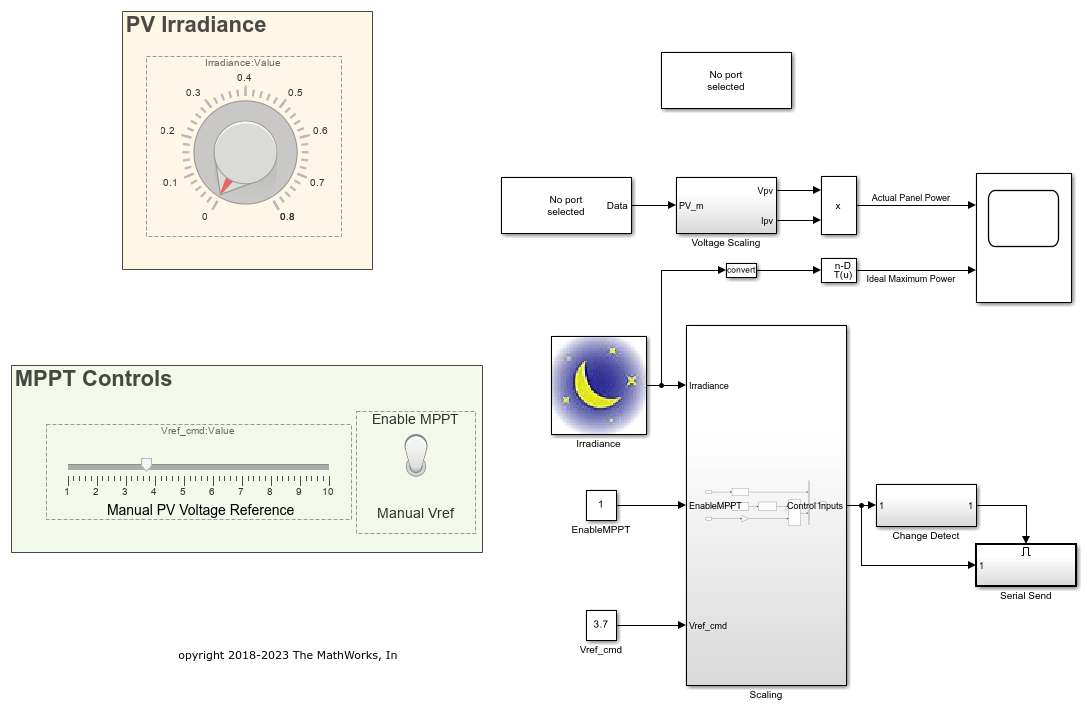

Execution scheduling models based on timer interrupts do not meet the requirements of some real-time applications to respond to external events. The C28x Hardware Interrupt block addresses this problem by allowing asynchronous processing of interrupts triggered by events managed by other blocks in the C28x DSP Chip Support Library.

When the C28x Hardware Interrupt block has an external interrupt selection, the selection enables interrupts on the selected general-purpose I/O pins. To configure these pins, see the Configuration Parameters > Hardware Implementation > Hardware board settings > Target hardware resources > External Interrupt pane. For more information, see Model Configuration Parameters for Texas Instruments C2000 Processors.

The task priority indicates the relative importance of the tasks associated with the asynchronous interrupts. The lowest value in this field represents the highest priority. The default priority value of the base rate task is 40, so the priority value for each asynchronously triggered task must be less than 40 (to configure them as higher-priority) for these tasks to preempt the base rate task.

The preemption flag determines whether a given interrupt is preemptable or not. Preemption overrides prioritization, if an interrupt triggers a higher-priority task while a lower-priority task is running, the execution of the lower-priority task can be suspended and resumed after the completion of the higher priority task, provided the lower-priority task is configured as preemptable.

Vectorized Output

The output of this block is a function call. The size of the function call line equals the number of interrupts the block is set to handle. Each interrupt is represented by four parameters shown on the dialog box of the block. These parameters are a set of four vectors of equal length. Each interrupt is represented by one element from each parameter (four elements total), one from the same position in each of these vectors.

Each interrupt is described by:

CPU interrupt numbers

Peripheral Interrupts Expansion (PIE) interrupt numbers

Task priorities

Preemption flags

Examples

Ports

Input

Output

Parameters

Version History

Introduced in R2016b