Clocking and Multirate Design

Generate HDL code for multirate models with single or multiple clocks and clock control elements, such as clock resets and timing controllers.

Topics

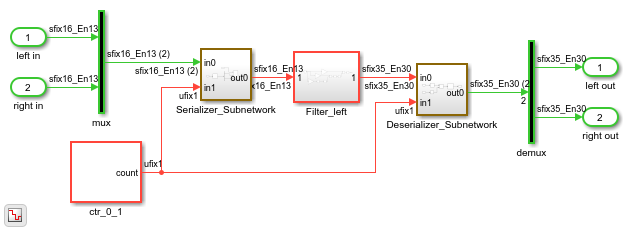

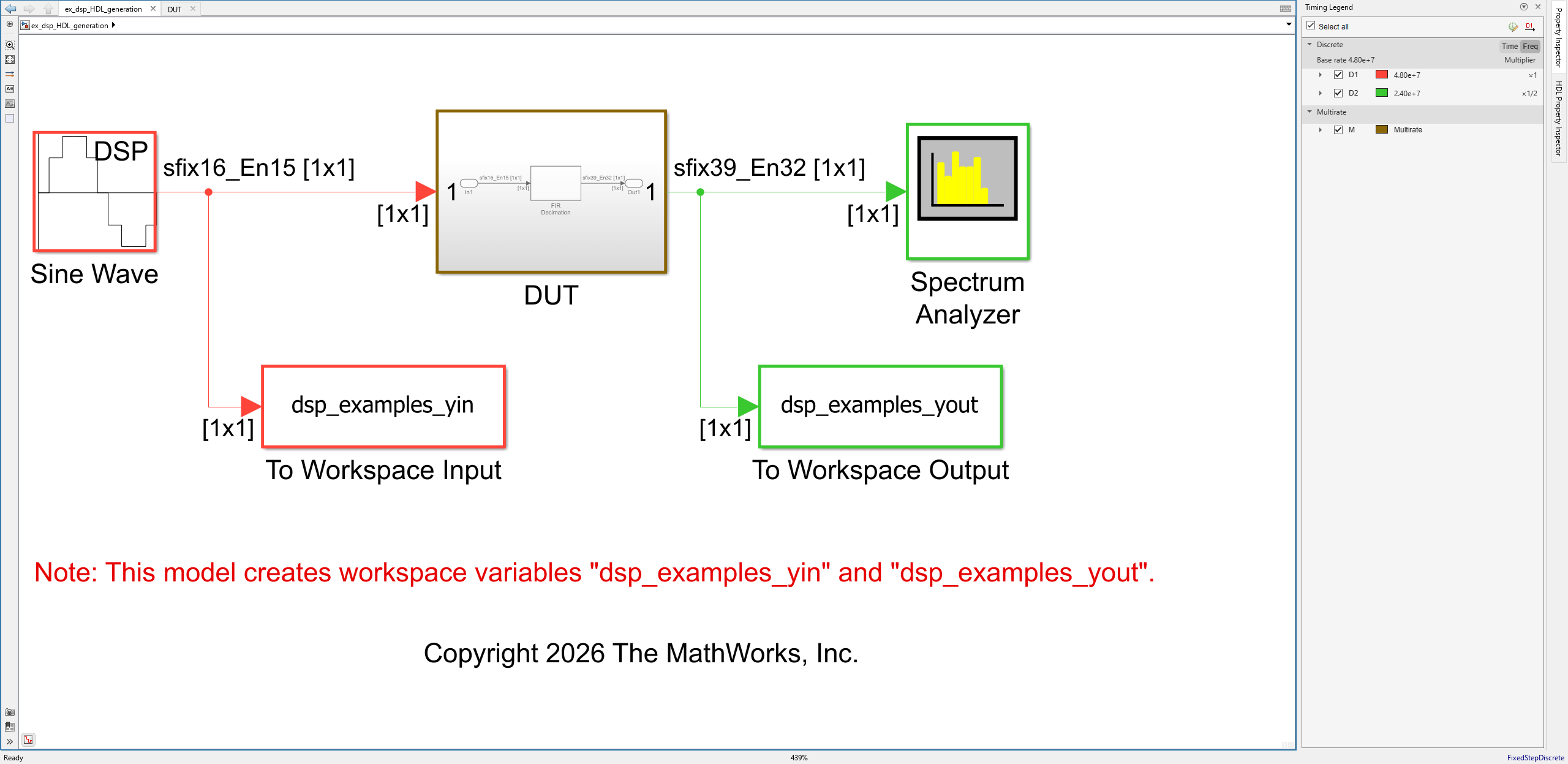

- Code Generation from Multirate Models

Overview of HDL code generation for single-clock, single-tasking multirate models.

- Generation of Clock Bundle Signals in HDL Coder

How HDL Coder™ generates clock, reset, and clock enable signals in the HDL code.

- Generate a Global Oversampling Clock

Generate a global oversampling clock to integrate your DUT into a larger design.

- Multirate Model Requirements for HDL Code Generation

Guidelines for setting up multirate models and blocks for HDL code generation.

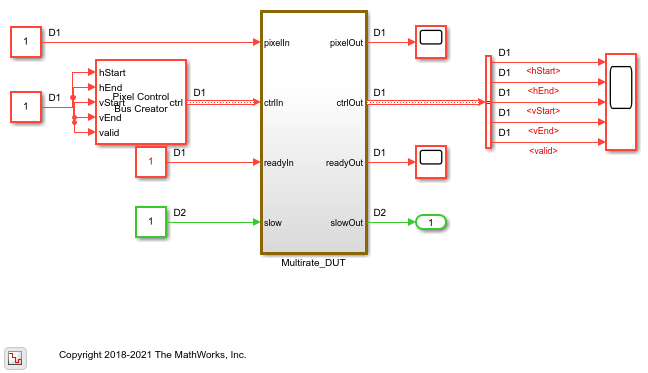

- Timing Controller for Multirate Models

Learn about timing controllers and clock enables in a multirate model.

- Generate Reset for Timing Controller

How to generate reset for timing controller.

- Use Triggered Subsystem in HDL Code Generation

Best practices for using Triggered Subsystems, Trigger As Clock setting in HDL code generation.

- Use Triggered Subsystem for Asynchronous Clock Domain

Design a model for an asynchronous clock domains using triggered subsystems.

- Generate Clock Enable Signals

Generation of clock enable signals in your DUT for single rate and multirate models.

- Customize Clock Bundle Names in Generated Code

Learn how to customize clock bundle names in the generated code.