Verify Model Simulation by Using when Decomposition

In a Test Assessment block, you can define the simulation condition that

activates a step that contains a verify statement by using a

when decomposition sequence. In a when

decomposition sequence, steps activate based on the simulation conditions that you define.

For more information about when decomposition sequences, see Test Sequence Basics.

verify statements evaluate logical expressions and return a

pass, fail, or untested result

for each time step and for the overall simulation. A fail result at

any time step results in a fail result

for the overall simulation. If no failing results occur, a

pass at any time step results in a

pass result for the overall simulation. Otherwise, the overall result

is untested. You can then review the test results in the Test

Manager or the Simulation Data Inspector if you run the simulation without a test

case. You can choose to display only pass and fail

statements by logging only tested verify statement results. For more

information on authoring verify statements, see verify.

You can author verify statements in a when decomposition:

If your model does not use a Test Sequence block as a source, or your test sequence steps do not correspond with the conditions to verify. In this situation, you can activate each

verifystatement using a signal condition.If your model uses a Test Sequence block as a source. In this situation, you can activate the

verifystatements in a Test Assessment block by using the active Test Sequence block step. See Use Active Step Output as Input to Another Block.

Activate verify Statements by Using Signal Conditions

This example shows how to use verify statements in a when decomposition in a Test Assessment block to author assessments in a test harness.

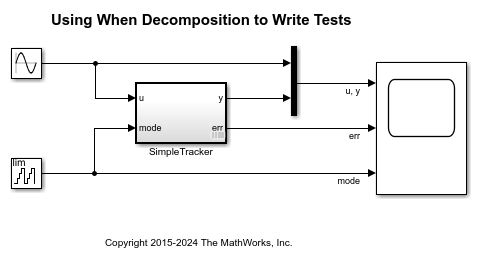

This model implements a simple signal tracker that operates in three modes: off, slow, and quick.

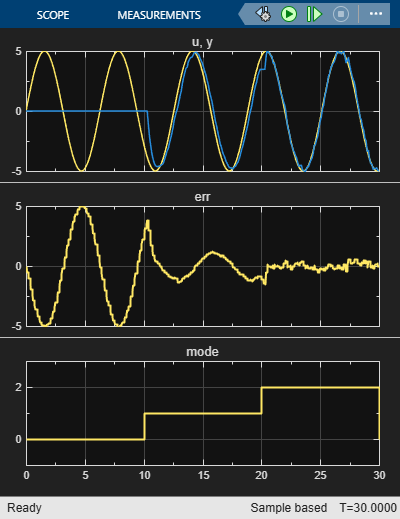

To observe the output and error signals, simulate the model.

Open the Test Harness

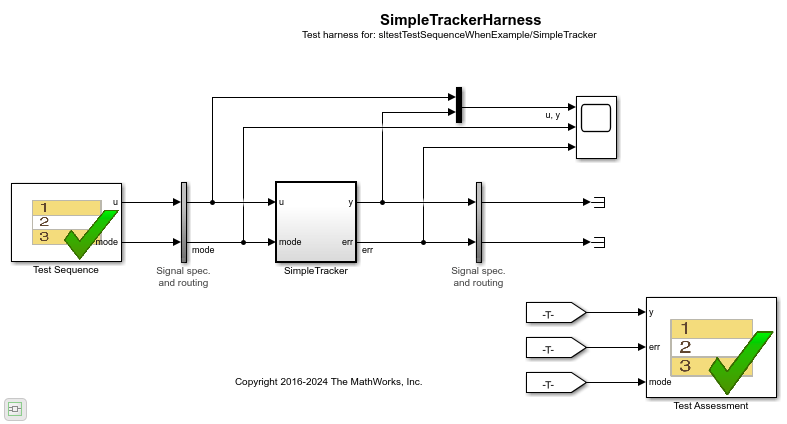

The SimpleTracker subsystem contains a test harness that contains a Test Assessment block.

The Test Assessment block assesses the behavior of the SimpleTracker subsystem by using verify statements in a when decomposition.

The CheckError step has a when decomposition with three substeps:

OffModeis active when the value ofmodeis0.SlowModeis active when the value ofmodeis1.QuickModeis active for all other values ofmode.

Run the Model Assessments

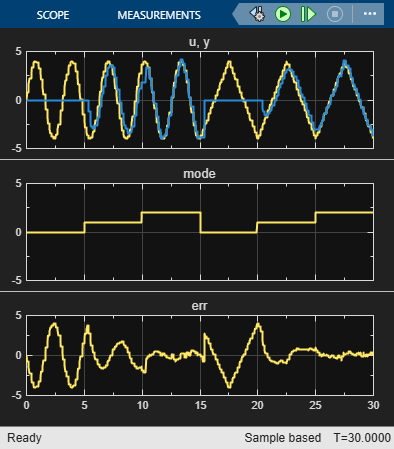

To run the assessments, simulate the test harness. Open the Simulation Data Inspector to inspect the results.

Log Only Tested verify Results

To log and display only pass and fail results, in the Harness tab, click Suppress Untested Results. Simulate the test harness and open the Simulation Data Inspector. The Simulation Data Inspector does not display the untested results.

Activate verify Statements by Using Test Sequence Steps

If your model uses a Test Sequence as a block source, you can connect the Test Sequence and Test Assessment blocks by using the active step signal from the Test Sequence block. You can create a when decomposition in the Test Assessment block and define verify statements to assess the model simulation.

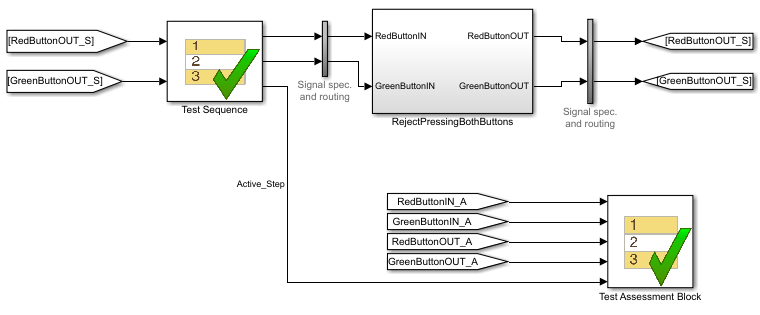

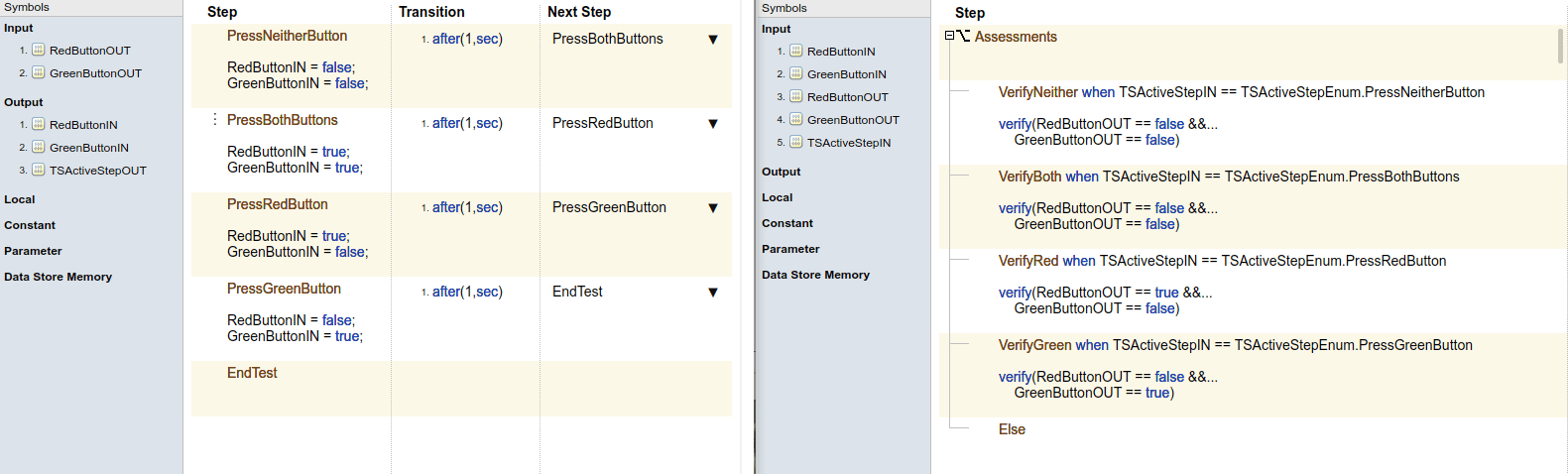

For example, the Harness1_TestSeqAndTestAssessment harness contains a Test Sequence and Test Assessment block. The Active_Step signal connects the blocks.

The Test Assessment block contains a when decomposition sequence with four substeps. Each substep contains a verify statement that evaluates two logical expressions. Each verify statement activates with a different Test Sequence block step.

The Else step in this example has no actions and handles the simulation conditions that do not match any of the preceding when conditions. This step cannot contain a when condition.

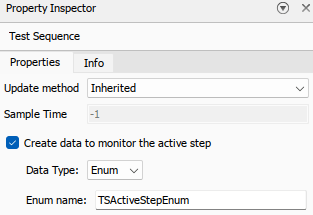

To activate the verify statements in a Test Assessment by using the active steps in a Test Sequence block, create active step data output for the Test Sequence block. On the Modeling tab, in the Design gallery, select Property Inspector. Then, select the Test Sequence block, and in the Property Inspector, select Create data to monitor the active step and set the Data Type to Enum. Enter a name in Enum Name.

Then, create an input data for the Test Assessment block. Open the Test Assessment block, and, in the Symbols pane, point to Input, click Add data ![]() , and name the input. Connect the Test Sequence block output to the Test Assessment block input.

, and name the input. Connect the Test Sequence block output to the Test Assessment block input.

Create a when decomposition in the Test Assessment block. By default, the Test Assessment block has a when decomposition sequence. To change between a standard sequence and a when decomposition sequence, right-click the parent step and select When decomposition. For each when decomposition step, define when the step is active by using the active step enumeration data.

VerifyBoth when TSActiveStepIN == ... TSActiveStepEnum.PressBothButtons

See Also

Test Sequence Editor | Test Sequence | Test Assessment | verify | sltest.testmanager.Assessment | sltest.testmanager.AssessmentSymbol | sltest.testmanager.TestCase