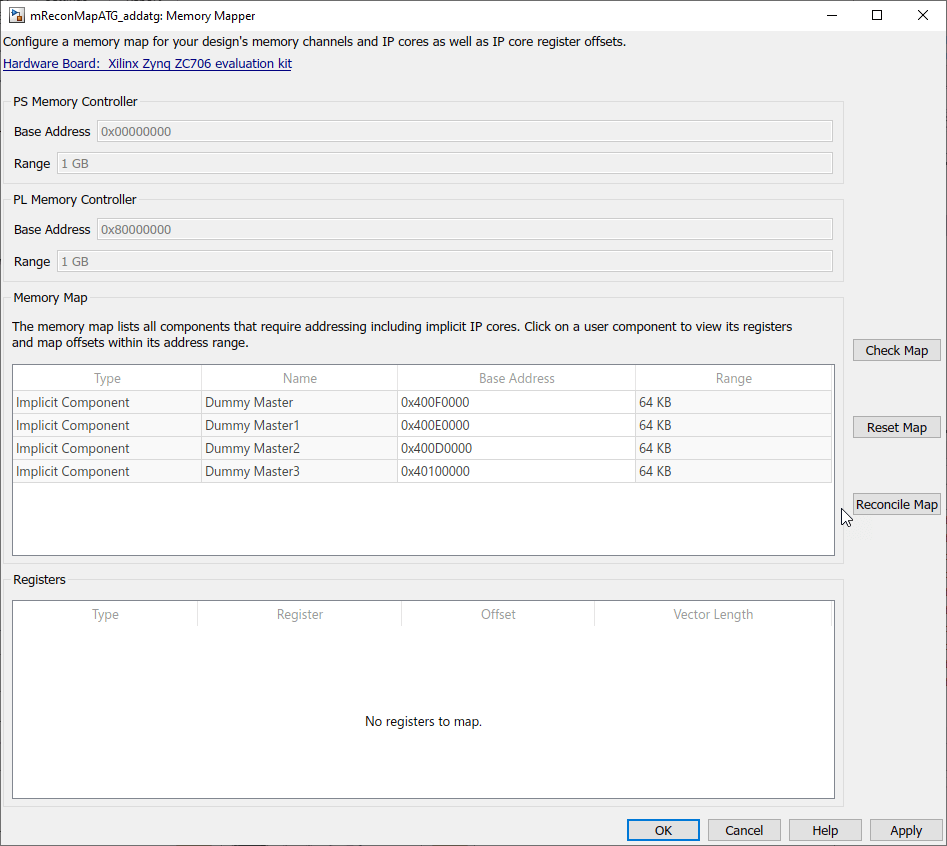

Memory Mapper

Configure memory map for SoC application

Description

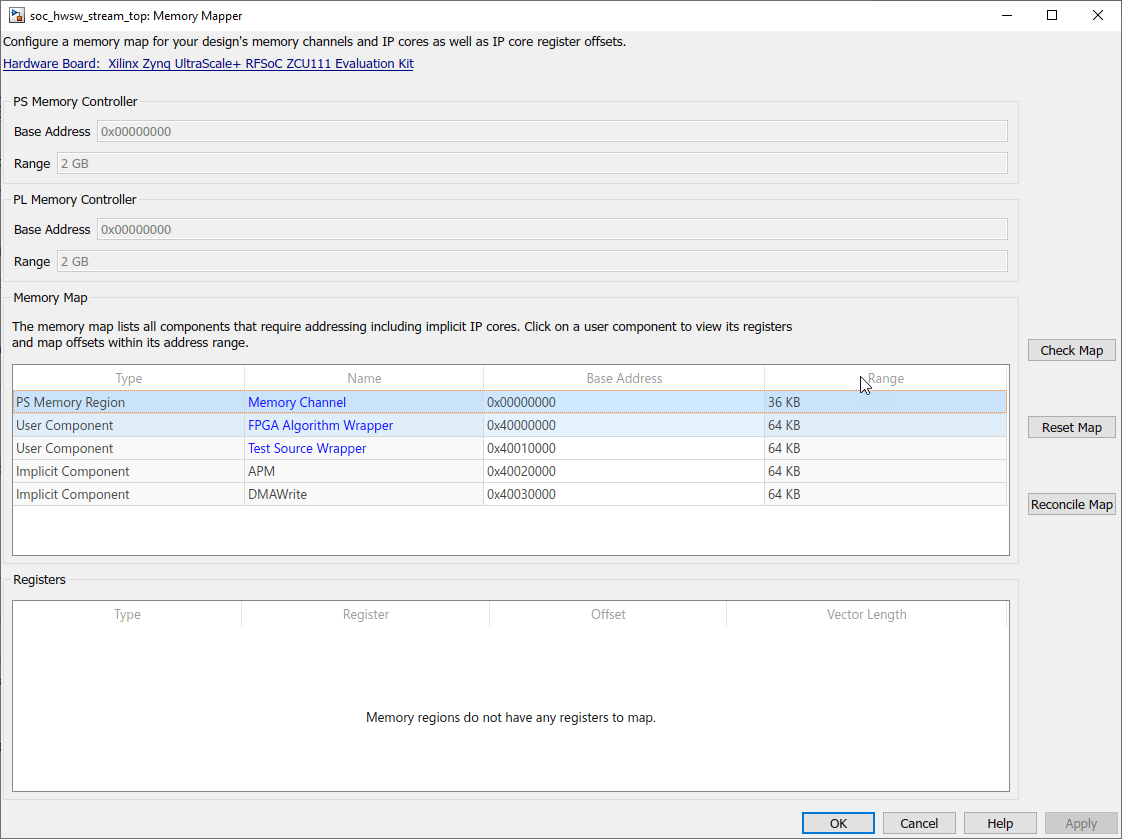

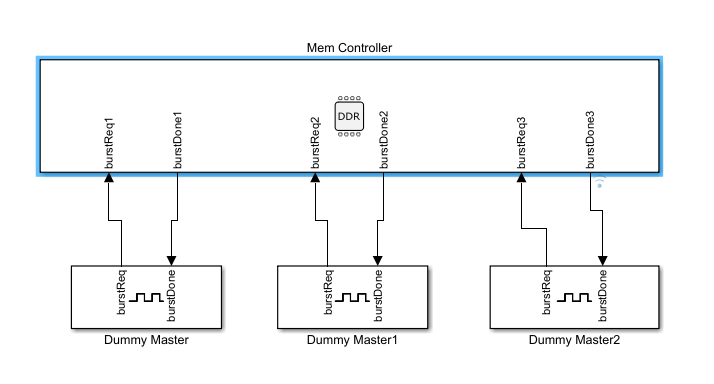

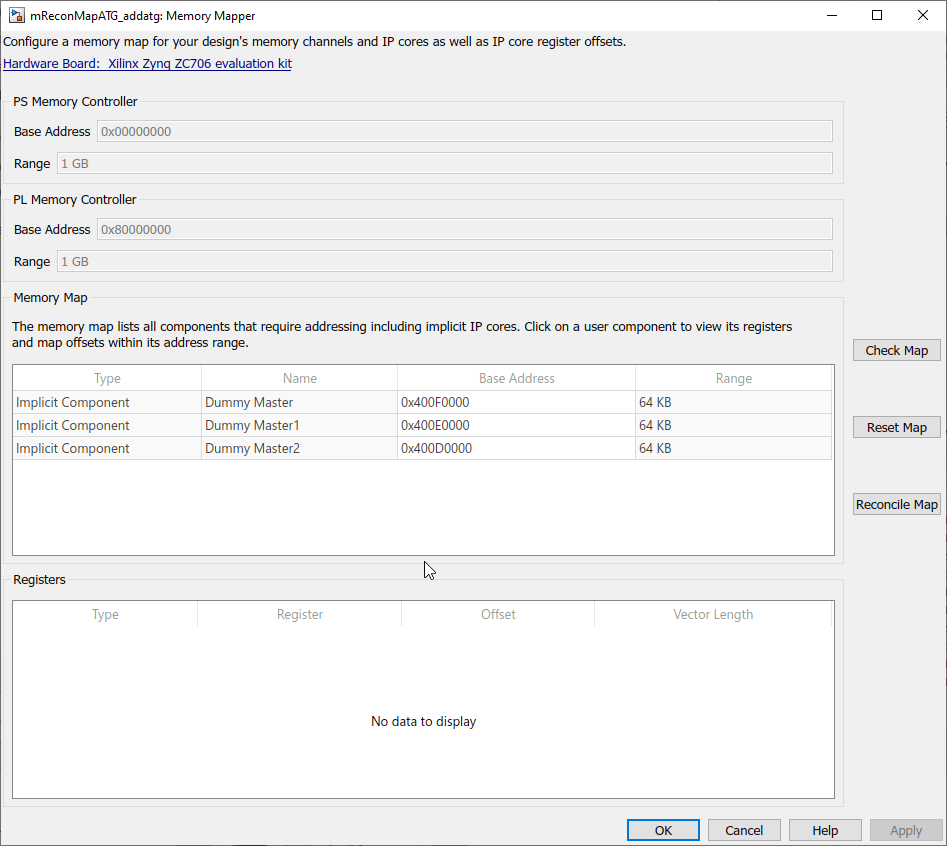

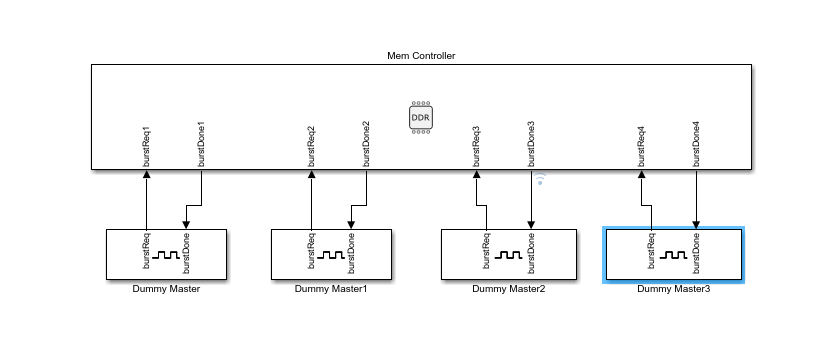

View and edit memory regions of an SoC application. Edit device base addresses and offsets for memory-mapped devices.

Using the Memory Mapper tool, you can:

View and edit base addresses, offsets, and memory locations of various channels and memory-mapped components in your design.

Check the memory map of your model for any conflicts between different memory channel configurations.

Reset the memory map to its default settings.

Reconcile an edited map to match model settings.

Open the Memory Mapper

In the Configuration Parameters dialog box, select Hardware Implementation from the left pane. Under Target hardware resources, select FPGA design (top-level) and click View/Edit Memory Map.

In the SoC Builder tool, in the Review Memory Map section, click View/Edit.

Parameters

Version History

Introduced in R2019a