LDPC Encoder

Libraries:

Wireless HDL Toolbox /

Error Detection and Correction

Description

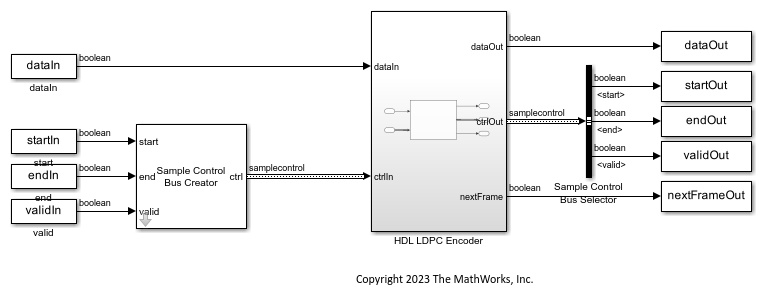

The LDPC Encoder block implements a quasi-cyclic low-density parity-check (QC-LDPC) encoder with hardware-friendly control signals. The block accepts data bits and a stream of control signals and outputs encoded bits, a stream of control signals, and a signal that indicates whether the block is ready to accept new inputs.

The block supports scalar inputs and vector inputs with a specified parity-check matrix and block size. The block also supports lower-triangular or upper-triangular, dual-diagonal, and mixed-diagonal parity-check matrices. The block supports LDPC codes of circulant weight 1. For more information, see Parity-Check Matrix.

You can use this block to develop a standard-based or generalized transmitter that uses a QC-LDPC for forward error correction (FEC) coding. The block provides an architecture suitable for HDL code generation and hardware deployment. See Algorithms.

Examples

Encode Data with Quasi-Cyclic Low Density Parity Check Code

Encode data bits with quasi-cyclic low-density parity-check codes.

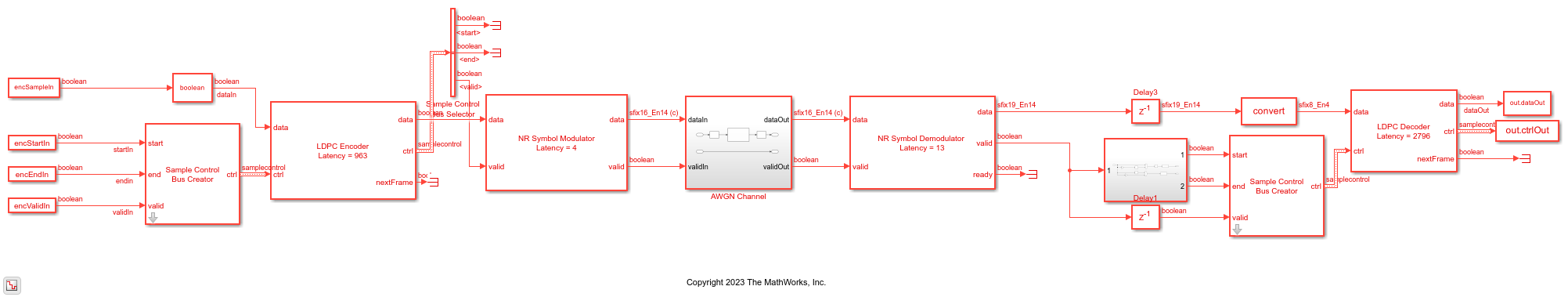

LDPC Encode and Decode of Streaming Data

Use LDPC Encoder and LDPC Decoder blocks and verify their functionality.

Ports

Input

Data bits, specified as a specified as a scalar or a column vector of size n, where n must be factor of Block size. The input data length must be (N–M) x Z, where M is the number of rows in the parity-check matrix, N is the number of columns in the parity-check matrix, and Z is the block size.

The size of the vector must be a factor of block size. In case of prime number block size, the supported vector sizes are 1 and block size itself.

Example: If block size is equal to 56, the supported vector sizes are 1, 2, 4, 7, 8, 14, 28, and 56.

Example: If block size is equal to 73, the supported vector sizes are 1 and 73.

Data Types: Boolean

Control signals accompanying the sample stream, specified as a

samplecontrol bus. The bus includes the start,

end, and valid control signals, which indicate the

boundaries of the frame and the validity of the samples.

start— Indicates the start of the input frameend— Indicates the end of the input framevalid— Indicates that the data on the input data port is valid

For more details, see Sample Control Bus.

Data Types: bus

Output

Encoded data bits, returned as a scalar or a column vector of size n, where n must be factor of Block size.

Data Types: Boolean

Control signals accompanying the sample stream, returned as a samplecontrol

bus. The bus includes the start, end, and

valid control signals, which indicate the boundaries of the frame

and the validity of the samples.

start— Indicates the start of the output frameend— Indicates the end of the output framevalid— Indicates that the data on the output data port is valid

For more details, see Sample Control Bus.

Data Types: bus

The block sets this signal to 1 when the block is ready to accept the start

of the next frame. If the block receives an input start signal

while nextFrame is 0, the block discards the

frame in progress and begins processing the new data.

For more information, see Using the nextFrame Output Signal.

Data Types: Boolean

Parameters

Specify a QC-LDPC parity-check matrix of size M-by-N, where M is the number of rows in the parity-check matrix and N is the number of columns in the parity-check matrix. N must be in the range [4, 128]. M must be less than N and must be in the range [3, N–1]. The last M columns of the parity-check matrix must be invertible in GF(2).

To learn more about the supported parity-check matrices, see Parity-Check Matrix.

Specify the block size. The block size must be an integer in the range [2, 512].

More About

QC-LDPC codes are an important class of codes within the family of LDPC codes. You can use LDPC codes in many applications because of their simple encoding implementation of using cyclic shift registers. The LDPC Encoder block performs encoding using a parity-check matrix.

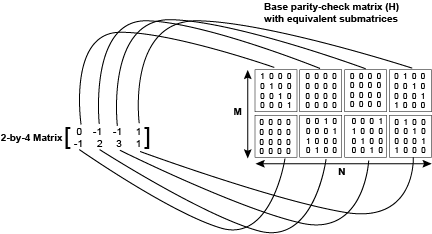

The block supports matrices with a circulant weight of 1. Each element in the parity-check matrix corresponds to a submatrix of size Z. The elements in the parity-check matrix must be in the range [–1, Z –1], where Z is the block size. In a parity-check matrix, –1 corresponds to a zero submatrix, 0 corresponds to an identity submatrix, 1 corresponds to an identity submatrix circularly shifted by one time, and n corresponds a submatrix circularly shifted by n times, where n is any value in the range [0, Z – 1].

This figure shows a parity-check matrix of size 2-by-4 whose block size is 4.

In this parity-check matrix:

–1represents a zero submatrix, [0 0 0 0; 0 0 0 0; 0 0 0 0; 0 0 0 0].0represents an identity submatrix, [1 0 0 0; 0 1 0 0; 0 0 1 0; 0 0 0 1].1represents an identity submatrix circularly shifted by one time, [0 1 0 0; 0 0 1 0; 0 0 0 1;1 0 0 0].2represents an identity submatrix circularly shifted by two times, [0 0 1 0; 0 0 0 1; 1 0 0 0; 0 1 0 0].3represents an identity submatrix circularly shifted by three times, [0 0 0 1; 1 0 0 0; 0 1 0 0; 0 0 1 0].

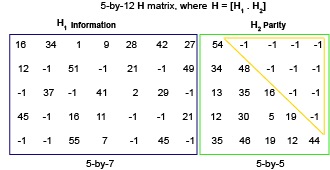

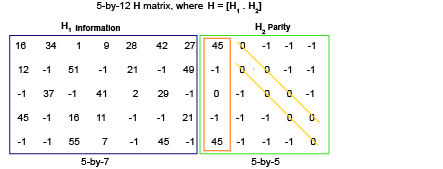

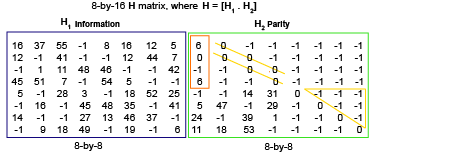

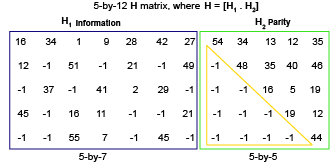

The parity-check matrix, H can be partitioned into two sub-matrices H1 and H2.

H = [H1 H2], where H1 is the information part of size M x (N – M) and H2 is the parity part of size M-by-M.

For example, in a parity-check matrix of size 5-by-12, the 5-by-7 submatrix H1 comprises the information part and the 5-by-5 submatrix H2 comprises the parity part, as this figure shows.

The LDPC Encoder block supports these types of parity-check matrix.

Lower-triangular — Contains –1s in the upper triangle of the parity part. These matrices are used in the IEEE 802.11ad and DOCSIS 3.1 cable communication standards.

Double-diagonal — Contains three nonzero elements in the first column of the parity part. Also, when you expand each element with an identity matrix of the block size, the sum over (GF2) of these elements must be an identity matrix, which means that at least two elements are the same. The remaining columns of the parity part must contain a bidiagonal pattern with 0s in its diagonals, and –1s in the rest of the parity part. These matrices are used in the Wi-Fi®, worldwide interoperability for microwave access (WiMAX), and wireless regional area network (WRAN) codes communication standards.

Mix of double-diagonal followed by a single-diagonal lower triangular — Contains a double-diagonal matrix with the extended rows and columns as a lower triangular part with 0s on the diagonals, and –1s in the rest of the parity part. These matrices are used in the 5G NR communication standard.

Upper-triangular — Contains –1s in the lower triangle of the parity part. These matrices are used in custom communications.

Algorithms

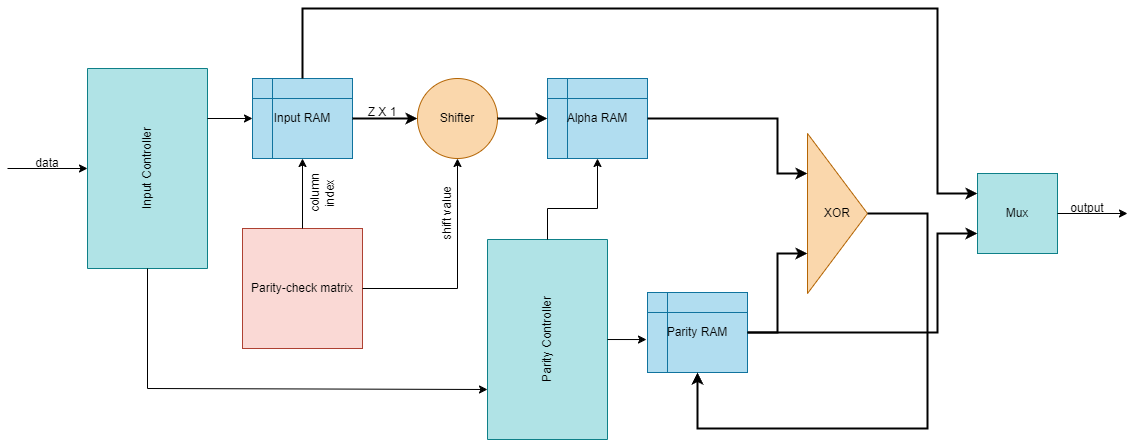

This figure shows the architecture block diagram of the LDPC Encoder block.

The Input Controller block reads and writes input data to the Input RAM block and enables the encoding after writing the entire frame to input RAM. The Parity-check matrix block consists of specified parity-check matrix values and provides shift values to the Shifter block. The Alpha RAM block stores the shifted output. The Parity Controller block calculates parity bit sequences and stores them in the Parity RAM block. The Mux block multiplexes and serializes the bits from the Input RAM and Parity RAM blocks.

The latency of the block varies with the Parity-check matrix parameter and the type of input. Because the latency varies, use the nextFrame control signal output port to determine when the block is ready for a new input frame.

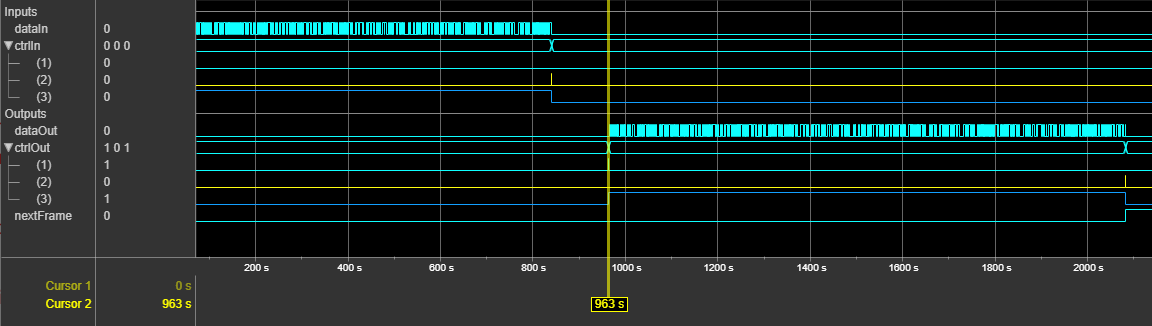

This figure shows a sample output and latency of the LDPC Encoder block for a scalar input when you use default settings for the block parameters. The latency of the block is 963 clock cycles.

The performance of the synthesized HDL code varies with your target and synthesis options. Performance also varies with the type of input, parity-check matrix, and block size.

This table shows the resource and performance data synthesis results of the block for both scalar and vector inputs with the default parameter configuration. The generated HDL is targeted to the AMD® Zynq®- 7000 ZC706 Evaluation Board.

| Input Type | Slice LUTs | Slice Registers | Block RAMs | Maximum Frequency in MHz |

|---|---|---|---|---|

| Scalar | 1608 | 1416 | 0 | 380.42 |

| Vector 56-by-1 | 1533 | 1527 | 1 | 330.62 |

This table shows the resource and performance data synthesis results of the block for

both scalar and vector inputs when you specify a dual-diagonal parity-check matrix of size

20-by-40 in the Parity-check matrix parameter and set the

Block size parameter to 128. The generated HDL

targets to the AMD

Zynq- 7000 ZC706 Evaluation Board.

| Input Type | Slice LUTs | Slice Registers | Block RAMs | Maximum Frequency in MHz |

|---|---|---|---|---|

| Scalar | 2453 | 2682 | 1 | 330.62 |

| Vector 64-by-1 | 2292 | 2773 | 0.5 | 350.26 |

Extended Capabilities

This block supports C/C++ code generation for Simulink® accelerator and rapid accelerator modes and for DPI component generation.

HDL Coder™ provides additional configuration options that affect HDL implementation and synthesized logic.

This block has one default HDL architecture.

| ConstrainedOutputPipeline | Number of registers to place at

the outputs by moving existing delays within your design. Distributed

pipelining does not redistribute these registers. The default is

|

| InputPipeline | Number of input pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| OutputPipeline | Number of output pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| SynthesisAttributes |

Specifies the synthesis attributes for the blocks and block output signals in the model. The generated HDL code contains these attributes. For more information, see SynthesisAttributes (HDL Coder). |

You cannot generate HDL for this block inside a Resettable Synchronous Subsystem (HDL Coder).

Version History

Introduced in R2023aThe LDPC Encoder block now supports column vector as input.

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Select a Web Site

Choose a web site to get translated content where available and see local events and offers. Based on your location, we recommend that you select: .

You can also select a web site from the following list

How to Get Best Site Performance

Select the China site (in Chinese or English) for best site performance. Other MathWorks country sites are not optimized for visits from your location.

Americas

- América Latina (Español)

- Canada (English)

- United States (English)

Europe

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)