Generate Custom Bitstream

To deploy a deep learning network to your custom target device, generate a custom

bitstream by using the dlhdl.ProcessorConfig object.

Create a

dlhdl.ProcessorConfigobject.hPC = dlhdl.ProcessorConfig;

Set up the tool path to your design tool. For example, to set up the path to the Vivado® design tool, enter:

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath','C:\Xilinx\Vivado\2023.1\bin\vivado.bat');

Generate the custom bitstream.

dlhdl.buildProcessor(hPC);

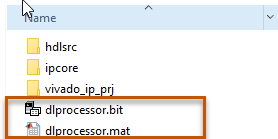

Locate the bitstream file and associated MAT file at

cwd\dlhdl_prj\, wherecwdis your current working folder. The name of the bitstream file isdlprocessor.bit. The name of the MAT file isdlprocessor.mat.To use the generated bitstream for the supported Xilinx® boards, copy the

dlprocessor.bitanddlprocessor.matfiles to the present working folder.

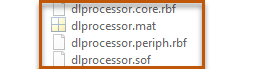

To use the generated bitstream for the supported Intel® boards, copy the

dlprocessor.core.rbf,dlprocessor.mat,dlprocessor.periph.rbf, anddlprocessor.soffiles to the same present working folder.

Deploy the custom bitstream and deep learning network to your target device.

hTarget = dlhdl.Target('Xilinx'); net = resnet18; hW = dlhdl.Workflow('Network',net,'Bitstream','dlprocessor.bit','Target',hTarget); % If your custom bitstream files are in a different folder, use: % hW = dlhdl.Workflow('Network',snet,'Bitstream',... % 'C:\yourfolder\dlprocessor.bit','Target',hTarget); hW.compile; hW.deploy;

See Also

dlhdl.ProcessorConfig | dlhdl.buildProcessor | dlhdl.Workflow