FIR Rate Converter

Upsample, filter, and downsample input signal

Libraries:

DSP HDL Toolbox /

Filtering

Description

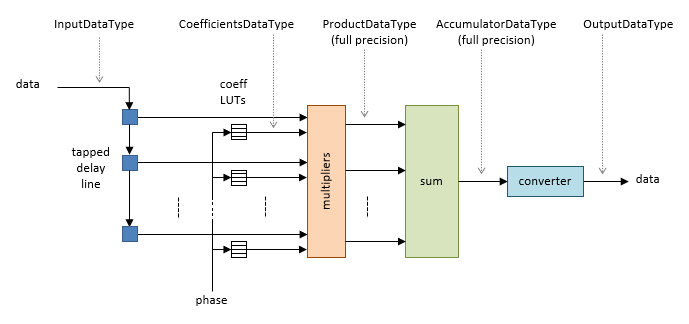

The FIR Rate Converter block upsamples, filters, and downsamples input signals. It is optimized for HDL code generation and operates on one sample of each channel at a time. The block implements a polyphase architecture to avoid unnecessary arithmetic operations and high intermediate sample rates.

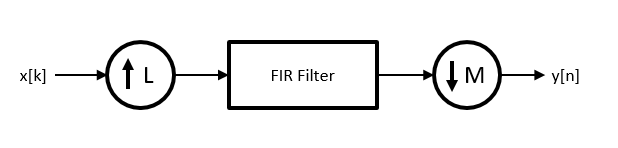

The block upsamples the input signal by an integer factor of L, applies it to a FIR filter, and downsamples the input signal by an integer factor of M.

You can use the input and output control ports to pace the flow of samples. In the default configuration, the block uses input and output valid control signals. For additional flow control, you can enable a ready output signal.

The ready output port indicates that the block can accept a new input

data sample. When L ≥ M, you can use the

ready signal to achieve continuous output data samples. If you apply a

new input sample each time the block returns ready signal as

1, the block returns a valid output sample on every time step.

When you disable the ready port, you can apply a valid data sample

only every ceil(L/M) time steps. For example, if:

L/M = 4/5, then you can apply a new input sample on every time step.

L/M = 3/2, then you can apply a new input sample on every other time step.

Note

You can also generate HDL code for this hardware-optimized algorithm, without creating a Simulink® model, by using the DSP HDL IP Designer app. The app provides the same interface and configuration options as the Simulink block.