Peripheral Management

Configure Infineon®

AURIX™ TC3x microcontrollers using blocks, peripheral app and configuration

parameter settings

Before communicating with target hardware, first apply block settings, hardware configuration parameters and Hardware Mapping tool settings.

Blocks

Tools

| SoC Builder | Build, load, and execute multicore application models on Infineon AURIX TC4x hardware boards (Since R2024b) |

| Hardware Mapping | Map tasks and peripherals in a model to hardware board configurations (Since R2022b) |

| Digital Port Read Peripheral Configuration | Map Digital Port Read peripherals in the Infineon AURIX model to peripheral registers in the MCU (Since R2024a) |

| Digital Port Write Peripheral Configuration | Map Digital Port Write peripherals in the Infineon AURIX model to peripheral registers in the MCU (Since R2024a) |

| Tasks | Map tasks in the Infineon AURIX to interrupt service routines on the hardware board (Since R2024a) |

| Encoder Peripheral Configuration | Map encoder peripherals in the Infineon AURIX model to peripheral registers in the MCU (Since R2024a) |

| EVADC Peripheral Configuration | Map EVADC peripherals in the Infineon AURIX model to peripheral registers in the MCU (Since R2024a) |

| PWM Peripheral Configuration | Map PWM peripherals in the Infineon AURIX model to peripheral registers in the MCU (Since R2024a) |

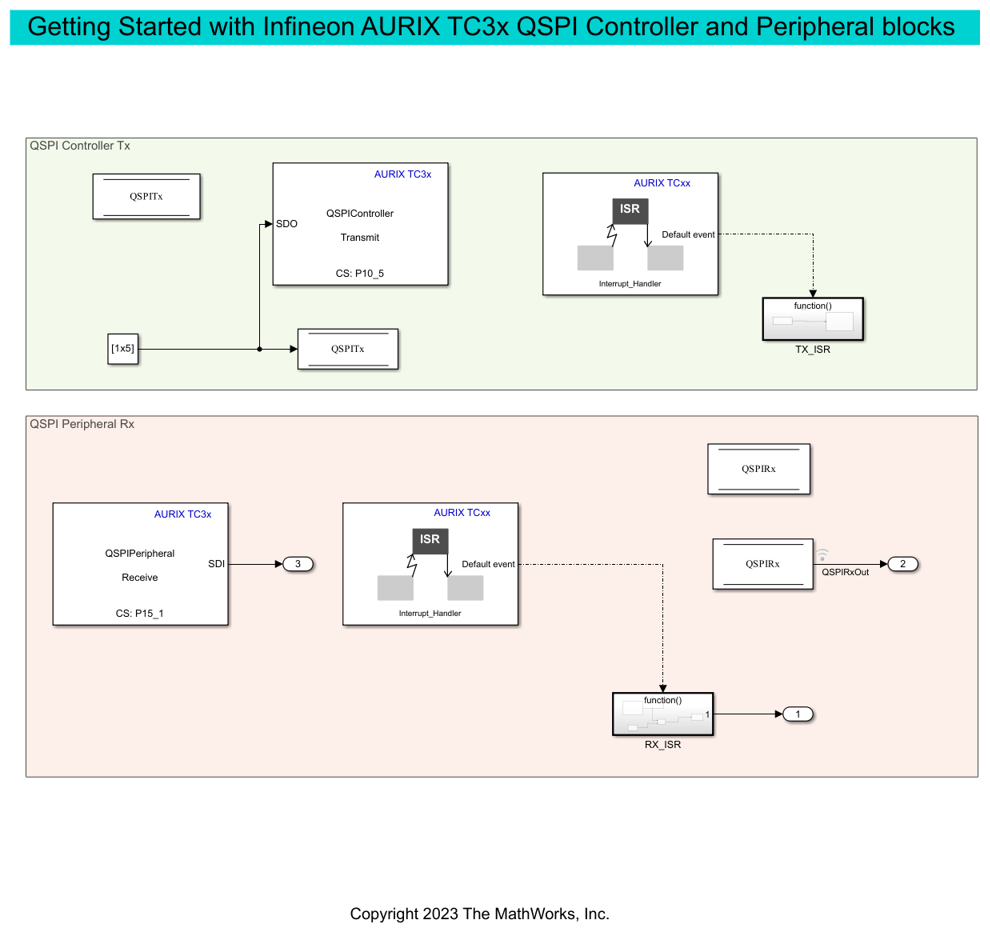

| QSPI Controller Peripheral Configuration | Map QSPI controller peripherals in the Infineon AURIX model to peripheral registers in the MCU (Since R2024a) |

| QSPI Peripheral Configuration | Map QSPI peripherals in the Infineon AURIX model to peripheral registers in the MCU (Since R2024a) |

| EDSADC Peripheral Configuration | Map EDSADC peripherals in Infineon AURIX model to peripheral registers in MCU (Since R2024b) |

| SENT Configuration | Map data transfer over SENT protocol in the Infineon AURIX model to peripheral registers in the MCU (Since R2024b) |

| MCAN Transmit Peripheral Configuration | Map peripherals of MCAN Transmit block in the model to peripheral registers in MCU (Since R2025a) |

| MCAN Receive Peripheral Configuration | Map MCAN Receive peripherals in the model to the peripheral registers in MCU (Since R2025a) |

Model Settings

Topics

- Run Model on Virtual Prototyping (VP)

Run your model on virtual prototyping without the hardware using the Synopsys Virtual Prototyping (VP) Virtualizer.

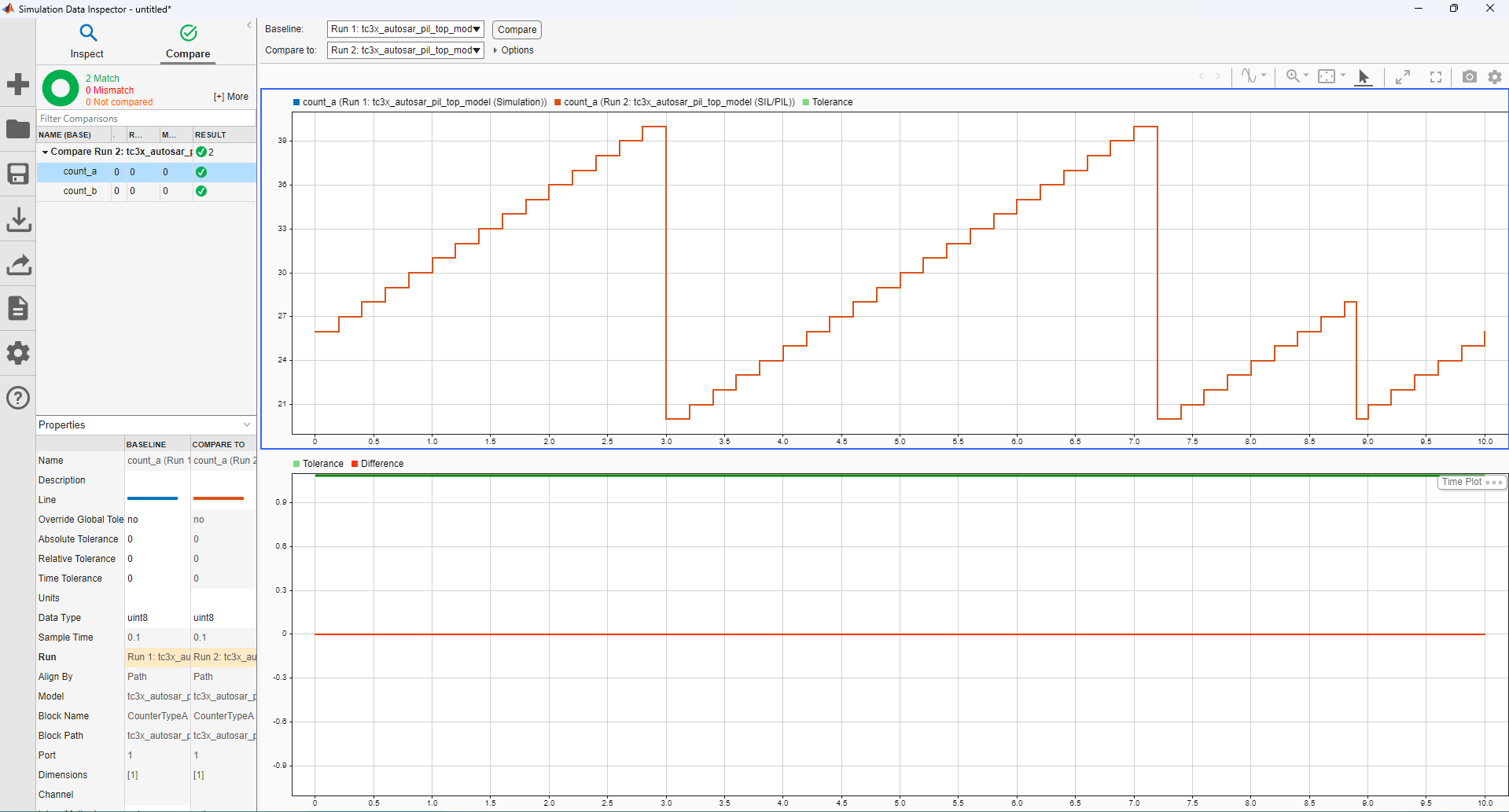

- Processor-in-the-Loop (PIL) Simulation

Test the code generated from top models, referenced models, or subsystems on Infineon AURIX TC3x microcontrollers.

- External Mode Simulation for Signal Monitoring and Parameter Tuning

Tune parameters and monitor signals through communication channel between development computer and Infineon AURIX TC3x microcontroller.

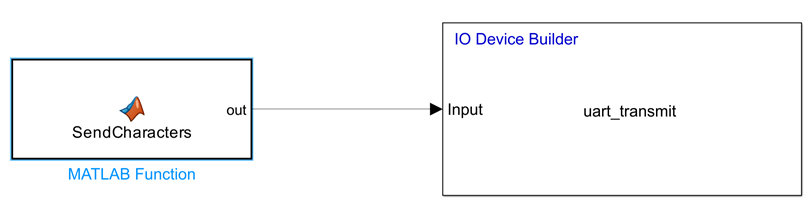

- Get Started with IO Device Builder

Understand system requirements and work with IO Device Builder.