Model Once, Deploy Anywhere: HDL and Embedded Coder Applied to Free Space Optics

Adam Herrmann, Altera

Roman Bogdanov, Altera

Designing free space optical (FSO) systems requires the development and integration of high-speed DSP algorithms, control systems, and interoperable control and communication protocols. While these components are implemented on different areas of the platform (ASIC, FPGA, or firmware), the interactions between them are critically important. These interactions need to be modeled and verified as early as possible to catch any interoperability and sequencing issues.

It is also desirable to maintain flexibility where these algorithms will run to avoid rework if the deployment target is changed.

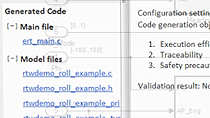

Explore how Altera developed a workflow centered around an architectural model for algorithm development and tuning written in MATLAB®, alongside a corresponding Simulink® model aimed at HDL generation using HDL Coder™. The models are structured so that the high-level implementation in MATLAB can be swapped for the implementation based in Simulink. This is a “shift-left, automate-right” approach applied to hardware verification allowing bugs to be identified and resolved prior to HDL code generation.

For firmware development, Altera used MATLAB to test functionality within the context of the overall system model. By leveraging emulated core plug-ins, they were able to verify firmware operation on the target hardware using processor-in-the-loop (PIL) simulation. This also kept deployment options flexible, as all that was needed to change the deployment target was to change the processor core selection in MATLAB.

Learn how Altera structured the model to make testing and deployment of each component simple, using MATLAB features such as the MATLAB Test Manager, build tool, projects, and class structures. You’ll see a demo showing how these different models tie together as part of a single simulation, allowing bugs to be found with ease by comparing MATLAB with Simulink on the fly. Additionally, see the addition of firmware-converted models seamlessly using PIL.

Recorded: 12 Nov 2025