Quality and stability improvements

R2025b delivers quality and stability improvements, building on the new features introduced in R2025a.

Model and Architecture Design

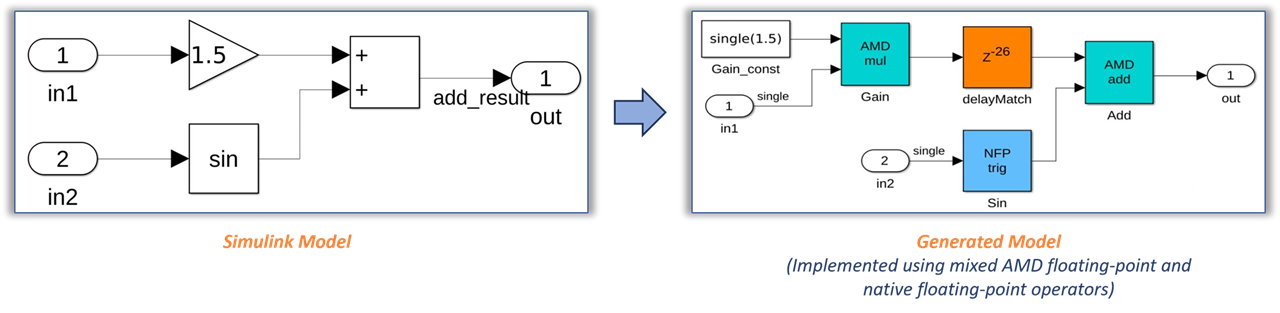

Generate HDL code for models that contain AMD blocks by using Vitis Model Composer

You can now generate integrated HDL code for models that contain AMD® blocks by using Vitis® Model Composer 2024.1 and HDL Coder™. HDL Coder generates HDL code from the Simulink blocks and uses AMD Vitis Model Composer to generate HDL code for the AMD blocks. For more information about Vitis Model Composer, see Vitis Model Composer on the AMD website.

Using Vitis Model Composer with HDL Coder allows you to use various performance-optimized AMD HDL blocks. Use this integration to iteratively explore designs, validate system-level functionality, or implement complex algorithms on AMD devices. You can use this functionality on Windows® operating system. For more information, See Generate Code for AMD Blocks by Using AMD Vitis Model Composer.

You can also generate IP cores for Versal Adaptive SoC devices that include AI Engines. To learn how to model, partition, and deploy a design that leverages the processor, FPGA, and AI Engines on a Versal device, see Integrate HDL IP Core with Versal AI Engine.

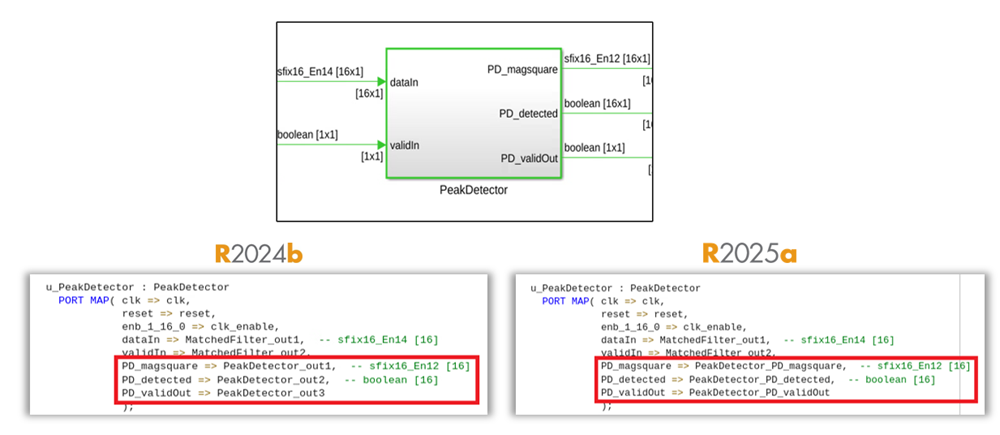

Improved output port naming in HDL code

Output ports for subsystems in generated code now follow the naming format

<SubsystemName>_<PortName>. Previously, HDL Coder used

the format

<SubsystemName>_out<PortNumber>

for naming the output ports. This enhancement improves readability and provides more

descriptive names for the output ports in the generated HDL code.

HDL Coder uses this output port naming for these subsystems:

Subsystem

Model Reference

Subsystem Reference

Variant Subsystem

Triggered Subsystem

Resettable Subsystem

Enabled Subsystem

Use buses with matrix types as inputs to Matrix Concatenate and Selector blocks

You can now generate HDL code for Matrix Concatenate block and Selector block when their input signals are buses containing matrix types. You can also use arrays of buses and nested arrays of buses at the input ports.

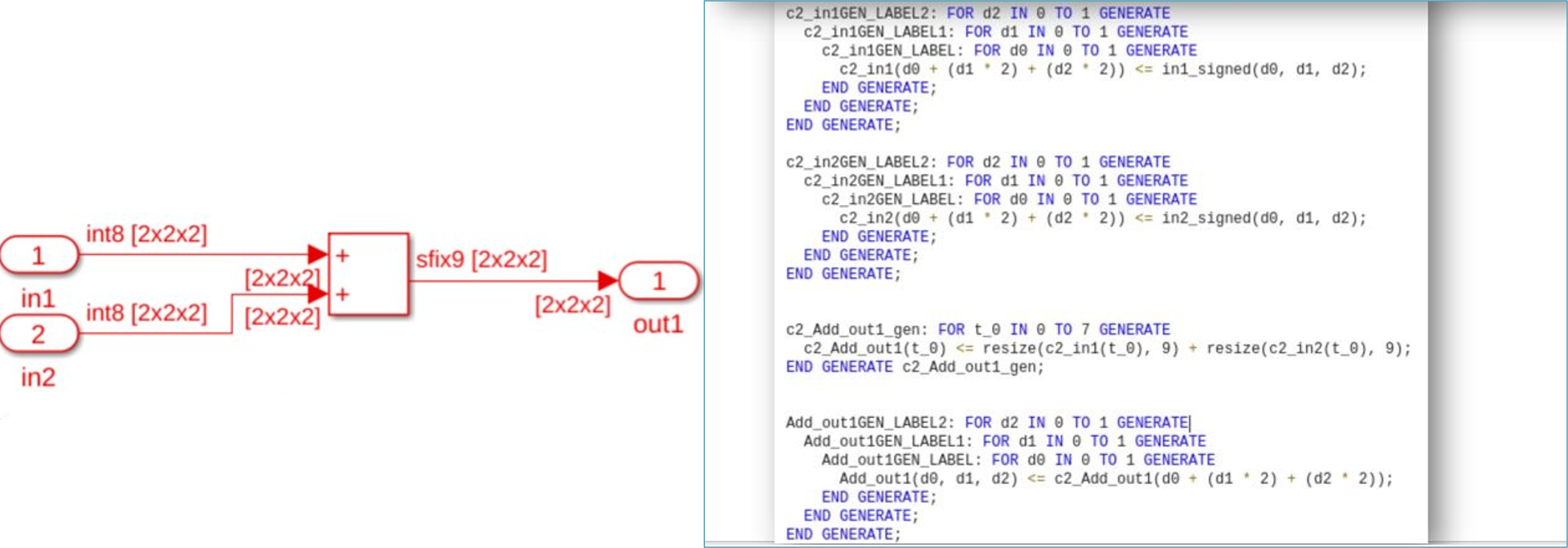

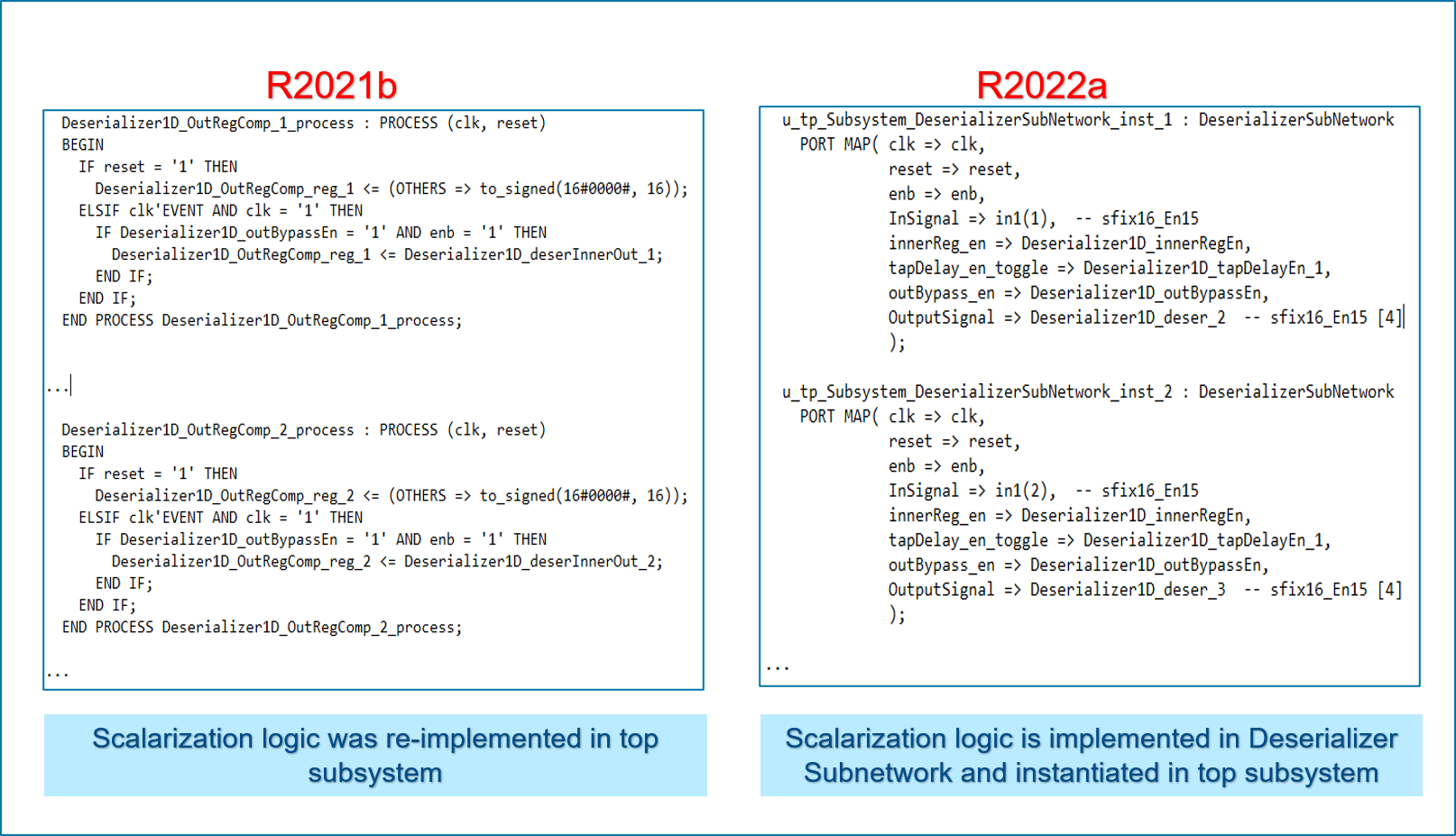

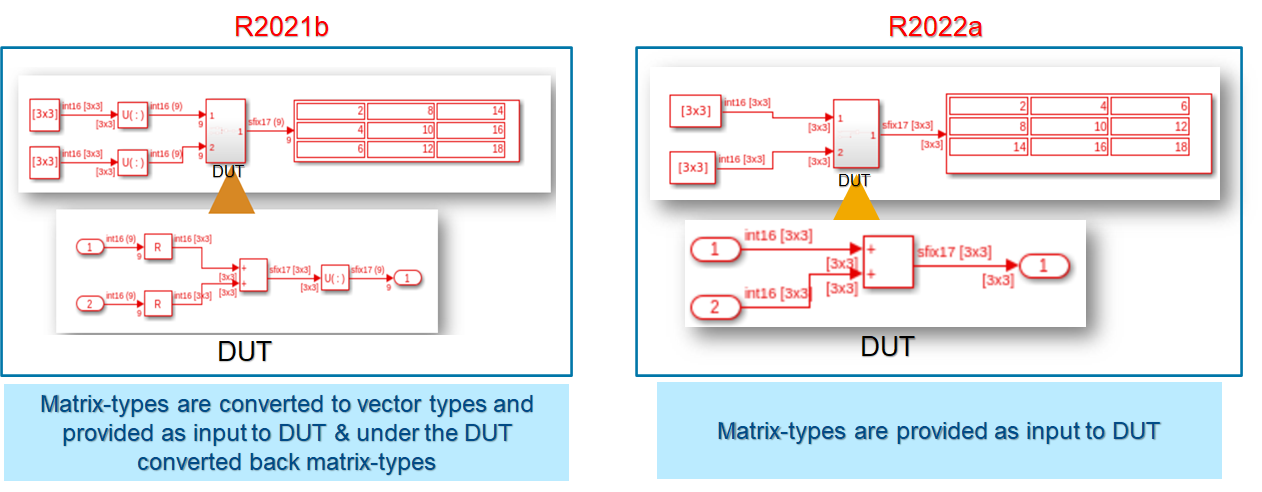

Generate code into multiple libraries for model references with vector or matrix input types

Prior to R2025a, when generating VHDL® or SystemVerilog code for model references with vector or matrix input types at the model boundary, you must scalarize the ports in the generated code or generate the code into a single library.

Starting in R2025a, you can generate VHDL or SystemVerilog code for model references with vector or matrix input types at the boundaries without scalarizing the ports. To generate the code into multiple libraries and avoid name-type conflicts of vector ports, clear the Generate VHDL or SystemVerilog code for model references into a single library configuration parameter option.

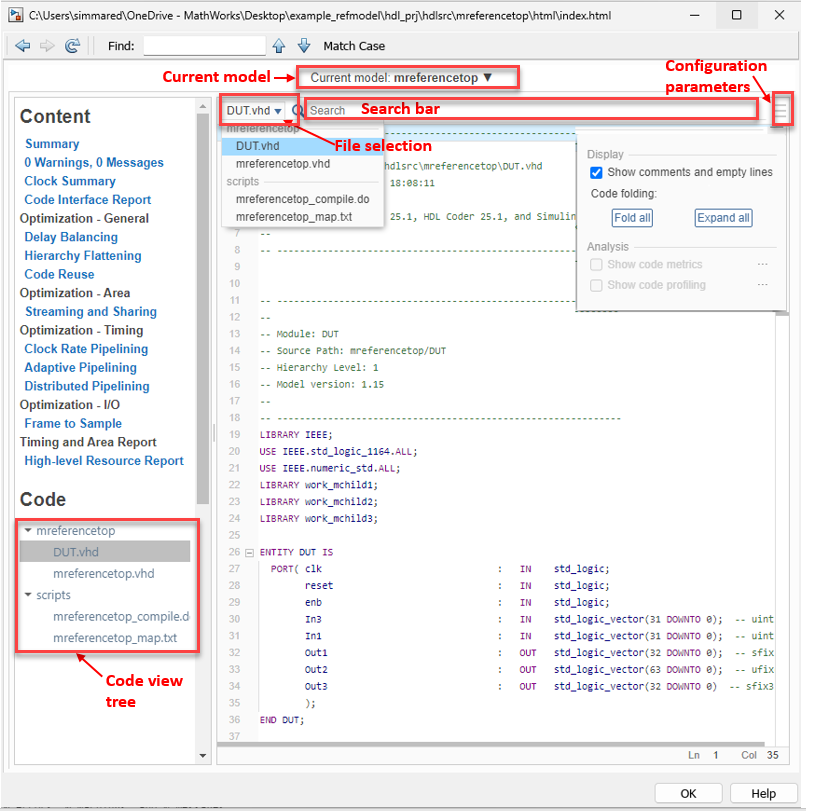

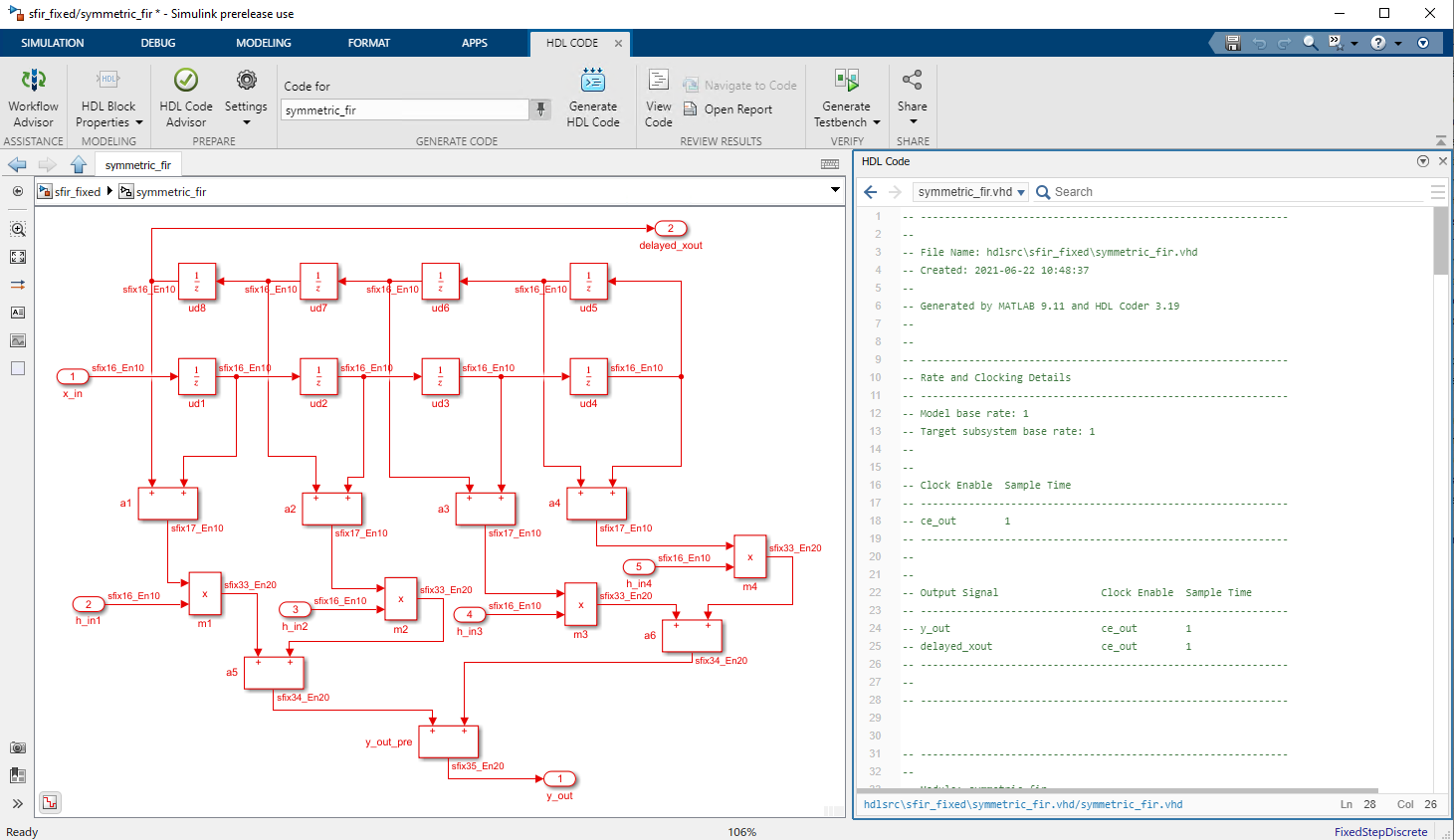

Improved formatting in Code Generation Report

Starting in R2025a, the code generation report has improved formatting when you generate code for a top-level subsystem block. The report includes these improvements:

A new layout for generated code files that allows you to select files, including a file selector, a search bar, and a configuration parameters button

that displays filters for the report.

that displays filters for the report.The new configuration parameter pane, which you can use to:

Show comments and empty lines in the generated code.

Collapse or expand all sections in the generated code by using the Code folding option.

A new Current model file selector at the top of code generation report pane, which you can use to select the top-level subsystem. To select a referenced model, click the model name to view the model hierarchy and make your selection.

A new search bar at the top of the right pane, which you can use to find or highlight text in the code.

The code view tree panel in the left navigation pane, which lists the source code and script files generated for the top-level subsystem. When you select a source code file, the right pane displays the corresponding source code. Alternatively, use the new file selector at the top of the right pane to choose the file you want to view.

The left navigation pane, which you can adjust for better usability.

Block Enhancements

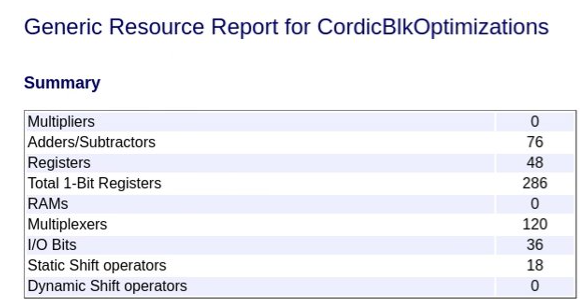

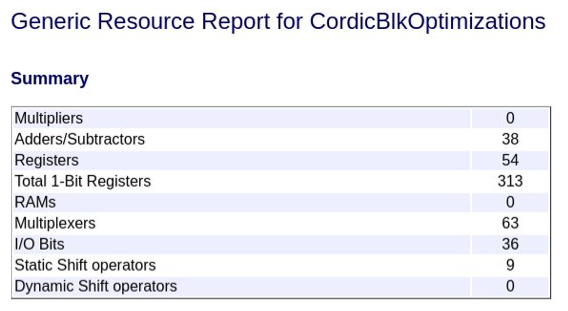

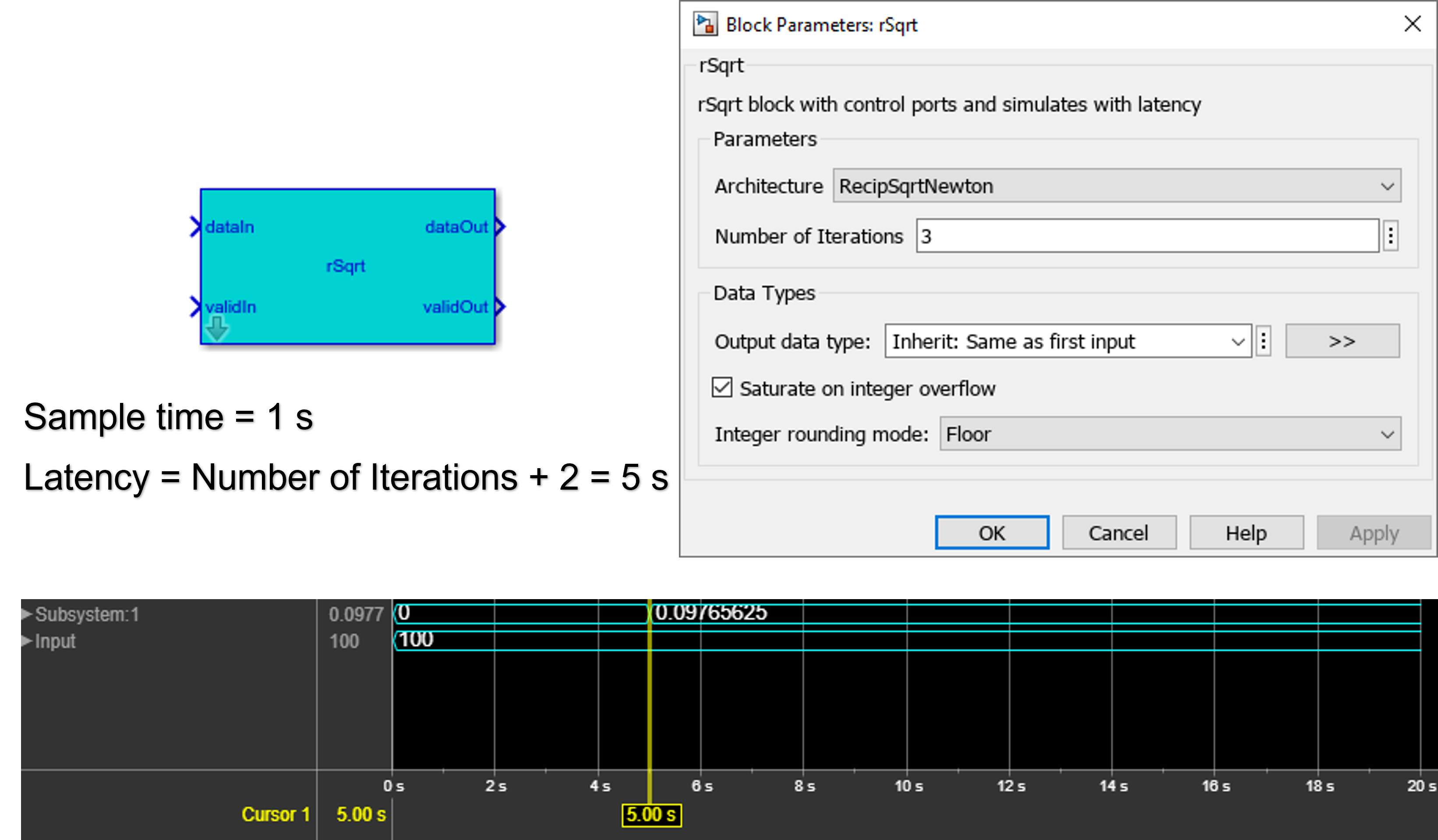

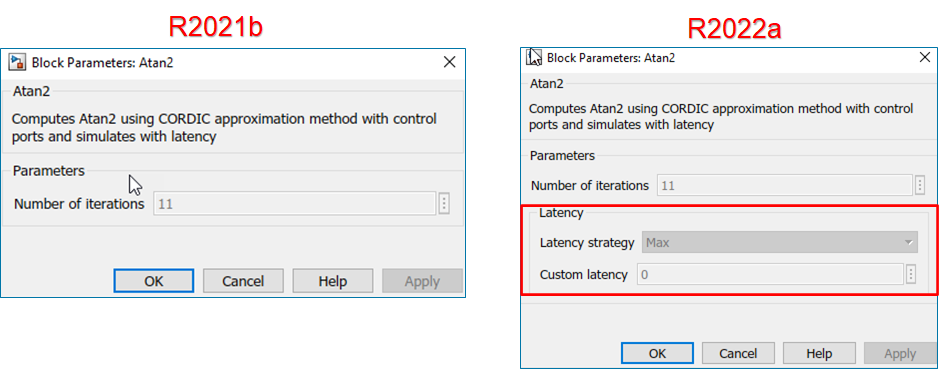

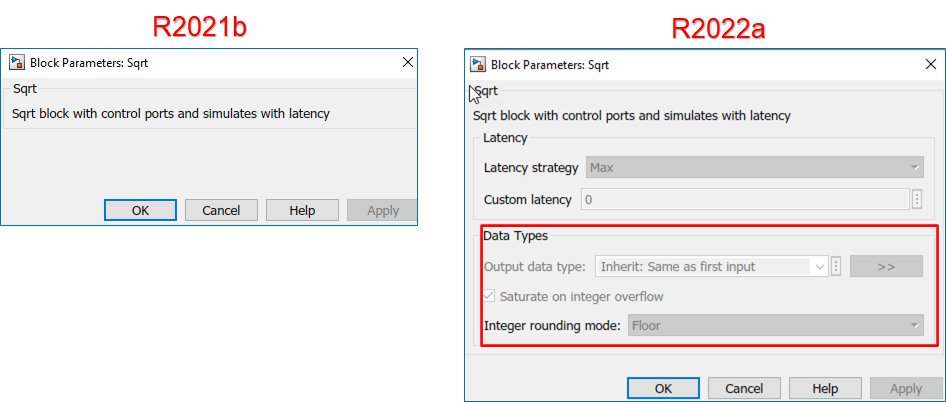

Control number of pipeline stages per iteration for blocks in HDLMathLib library and core math blocks

Blocks in the HDLMathLib library and core math blocks can now use a new

custom latency setting that enables you to control the pipeline stages for iterative

algorithms. Set the LatencyStrategy HDL block property to

Custom(PerIterations), then specify the number of pipeline

stages per iteration using the IterationsPerPipeline parameter. Use the

new setting to control the pipeline stages in the generated code and optimize the design for

speed and resource utilization. For more information, see IterationsPerPipeline.

This enhancement applies to all HDLMathLib library blocks and core

math blocks, including:

Set explicit breakpoints for n-D Lookup Table and Prelookup Table blocks

You can now generate HDL code for Prelookup and n-D

Lookup Table blocks that explicitly define breakpoint data. Set the

Breakpoints Specification parameter to Explicit

values and then specify the breakpoint data explicitly to each table

dimension of table data in Breakpoints row field. This enhancement

supports both fixed-point and floating-point data types for breakpoint data in n-D Lookup

Table blocks, and fixed-point data types in Prelookup blocks.

Additionally, HDL Coder improves the performance of Prelookup and n-D Lookup Table blocks

that use evenly spaced breakpoints. You can also use Linear

search and Binary search index search methods

for these lookup table blocks.

Use additional rounding modes for Divide and Reciprocal Blocks

You can now generate HDL code for additional settings of the Integer rounding

mode parameter of the Divide and Reciprocal blocks. Previously, HDL Coder

supported only the Zero and Simplest

settings for the Divide block and the Zero setting for the

Reciprocal block. You can now select from these additional rounding modes:

| Blocks | Integer Rounding Modes |

|---|---|

|

|

|

|

Select the appropriate rounding modes based on your design requirements to achieve optimal precision. The performance and hardware usage of each rounding mode vary.

Control vector input handling for RAM System blocks

Starting in R2025a, you can enable serial access for RAM System blocks by

setting the new Specify vector input access to

Serial. Enable serial access to design systems that can reconfigure

lookup operations after hardware deployment.

When you enable serial access and generate HDL code, the code generator does not scale up RAM consumption with the size of the vector input. Instead, it applies each operation of the input signals one at a time, starting with the first index. Enabling serial access allows you to leverage multicycle RAM access at a faster clock rate while modeling with a vector input at the data rate.

To enable Specify vector input access:

Clear the Model RAM with one cycle of delay parameter, or

Select the Use asynchronous read feature in target hardware parameter.

If the RAM System block exists in a clock-rate pipelining region, the serialization uses a clock-rate implementation instead of local multirate in the generated model.

For more information, see Manage How HDL Coder Maps RAM.

Functionality being removed or changed

HDL Reciprocal block has been removed

The HDL Reciprocal block has been removed. Instead, use the

Math Function block and set Function to

reciprocal. For more information, see the HDL Code

Generation section of the Math Function (R2025a) block.

Code Generation and Verification

Native floating-point for Stateflow charts

Native floating-point support in HDL Coder enables you to generate code from your floating-point design. If your design has complex math and trigonometric operations or has data with a large dynamic range, use native floating point. Starting in R2025a, HDL Coder supports code generation for Stateflow® charts with:

Floating-point constants

Floating-point inputs

Function calls with floating-point arguments

Floating-point arithmetic operations

These chart types are supported:

Classic charts

Mealy charts

State transition tables

Truth tables

Requirement tables

Conditionally triggered or enabled Stateflow charts and Moore charts are not supported.

For more information on generating HDL Code from your floating-point design, see Introduction to Stateflow HDL Code Generation and Native Floating Point Support for Simulink Blocks.

Generate HDL code with AMD and Intel floating-point libraries for MATLAB algorithms

You can now use the MATLAB to HDL Workflow Advisor to generate HDL code for your MATLAB® algorithms that utilize the AMD or Intel® floating-point operators and HDL Coder native floating point IPs. Use the AMD or Intel optimized floating-point operators to reduce your lookup table (LUT) and register resources. Before R2025a, you could only generate code that used AMD or Intel optimized floating-point IPs and HDL Coder native floating-point IPs from Simulink® models.

To generate code that incorporates both AMD or Intel floating-point operators and HDL Coder native floating-point operators, in the HDL Workflow Advisor:

Set the Synthesis tool parameter to

Xilinx Vivado,Altera Quartus II, orIntel Quartus Pro.Set the

VendorFloatingPointLibraryproperty of thecreateFloatingPointTargetConfigmethod toAMDFloatingPointOperatorsorAlteraFPFunctions.

Use this mixed-design approach to accommodate larger and more complex designs into your target device fabric. You can also use the AMD or Intel floating-point operators when you use the generic ASIC/FPGA workflow. See, Generate HDL Code from MATLAB Code by Using Native Floating-Point and Vendor Floating-Point Library IP.

New code generation reports for MATLAB-to-HDL code generation

Starting in R2025a, when you generate HDL code from MATLAB code, HDL Coder generates an HTML code generation report that contains information about:

Code interfaces

Adaptive and distributed pipelining

Delay balancing

Frame to sample

To enable code generation reports for MATLAB-to-HDL code generation, in the Workflow Advisor, enable these parameters in the Report Settings section:

Generate Report

Generate Resource report

Generate Optimization report

For more information about customizing the code generation reports, see Create and Use Code Generation Reports.

Alternatively, use the GenerateOptimizationReport and

GenerateResourceReport options for coder.config.

For more information, see coder.config, coder.HdlConfig, and Generate HDL Code from MATLAB Code Using the Command Line Interface.

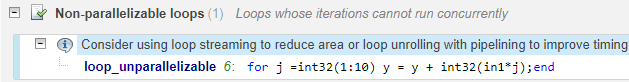

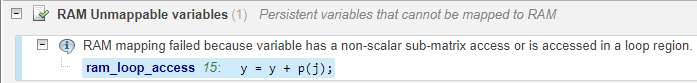

Access code insights during MATLAB-to-HDL code generation

Use code insights during MATLAB-to-HDL code generation to facilitate better understanding and usage of the code. Code insights are messages about potential issues in the generated code, such as potential differences in behavior from MATLAB code or potential row-major issues. These messages appear in the Code Insights tab of the code generation report.

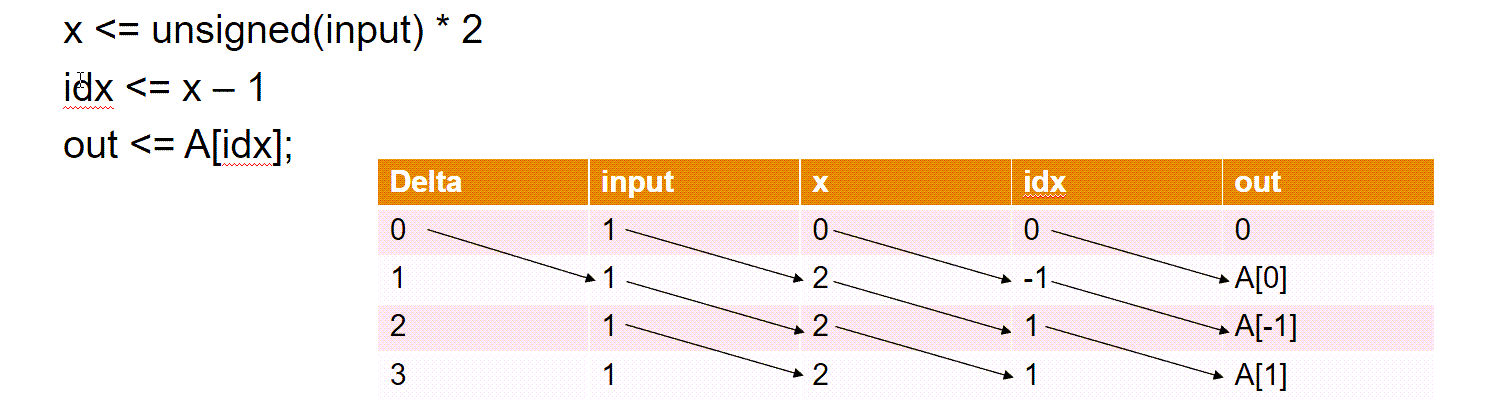

This image shows a code insight when you try and parallelize a non-parallelizable user-defined for-loop and there are no optimizations applied to the loop.

This image shows a code insight when you map to RAM and have a persistent variable access in a loop region.

Simulate HDL code generated from MATLAB algorithms in Vivado Simulator

You can now simulate HDL code generated from your MATLAB algorithms in the Vivado® Simulator environment. In the MATLAB-to-HDL Workflow Advisor, set the

Simulation Tool option to Xilinx Vivado

Simulator. HDL Coder generates the simulation scripts that you can use test your design in the

Vivado Simulator environment.

To test your design using the Vivado Simulator:

Set up the Xilinx Vivado synthesis tool using

hdlsetuptoolpathcommand.Open the HDL Workflow Advisor for your MATLAB HDL project.

In the Verification > Verify with HDL Test Bench step, select Generate test bench and Simulate generate test bench options and set the Simulation tool option to

Xilinx Vivado Simulator.To generate the test bench and simulate your design, click Run.

HDL Coder generates the simulation script that includes Tcl commands that load and compile the generated HDL code and test bench. It then uses the Vivado Simulator environment to execute these Tcl scripts and test your design. See Verify Code with HDL Test Bench.

Alternatively, you can run the generated simulation script directly on the Xilinx Vivado

tool. Select Tools > Run Tcl script. Browse to the folder that has

generated HDL and simulation script files, and select the

<projectName>_vivado_sim.tcl script. After the test completes, you

can view the simulation results in Vivado.

Use the Cadence Genus synthesis tool in the MATLAB-to-HDL workflow

You can now synthesize HDL code generated from your MATLAB algorithm by using the Cadence® Genus synthesis tool in the MATLAB-to-HDL Workflow Advisor.

To use the Cadence Genus Synthesis tool:

Use the

hdlsetuptoolpathcommand and specify Cadence Genus as the first argument and the path to the executable as the second argument.Open the HDL Workflow Advisor for your MATLAB HDL project.

In the HDL Workflow Advisor, in the Set Target > Set Target Device and Synthesis Tool step, to the right of Synthesis tool, click Refresh.

For more information on setting up HDL Workflow Advisor in MATLAB, see Workflows in HDL Workflow Advisor.

Speed and Area Optimizations

Improved latency budget checking for feedback loops

Starting in R2025a, if you enable pipelining within a feedback loop that has an insufficient latency budget, HDL Coder inserts the budgeted cycles of pipelines and generates a warning describing actions to take to increase the latency budget. The Delay Balancing report contains a table detailing the inserted pipelines and those pipelines which could not be inserted.

For more information on the delay balancing report, see Create and Use Code Generation Reports. For more information on modeling your design with latency, see Use Delay Absorption While Modeling with Latency.

Clock-rate pipelining support for Upsample block in multirate designs

In R2025a, when you use the clock-rate pipelining optimization, the Upsample (DSP System Toolbox) block does not act as a barrier to the optimization. As a result, clock-rate pipelining optimizes multirate designs more effectively by reducing the large amount of latency and unbalanced delays that could have previously occurred. For example, in previous releases, a multirate design with feedback loops might generate delay balancing errors when you enabled clock-rate pipelining. In R2025a, these designs do not generate delay balancing errors.

For more information, see Clock-Rate Pipelining.

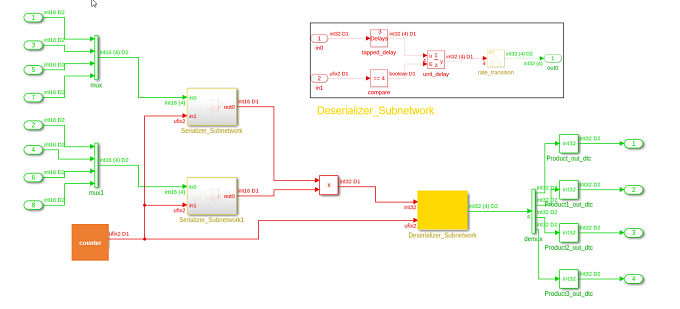

Improved reuse detection between Simulink subsystems

Starting in R2025a, HDL Coder can better detect reuse conditions for subsystems that:

Link to same library block,

Have identical HDL block parameters, and

Implement any of following characteristics:

Non-bus data types

Non-virtual buses

Virtual buses with all elements of the same built-in data type

For more information, see Generate Reusable Code for Subsystems.

In R2025a, HDL code you generate may implement more reusable HDL modules compared to previous releases.

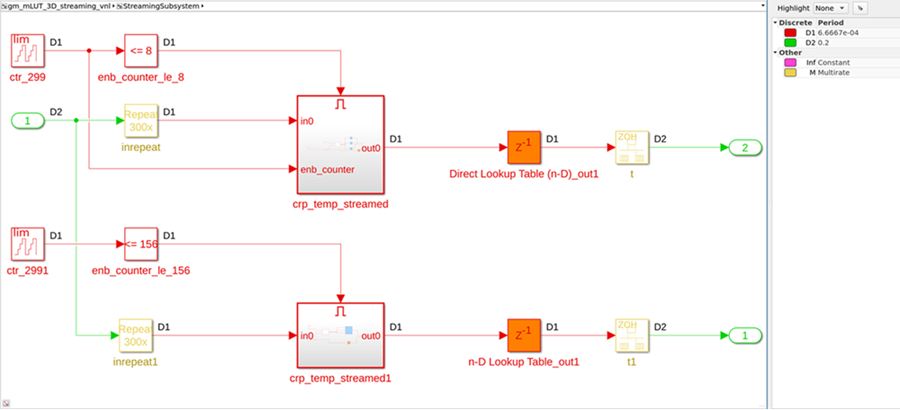

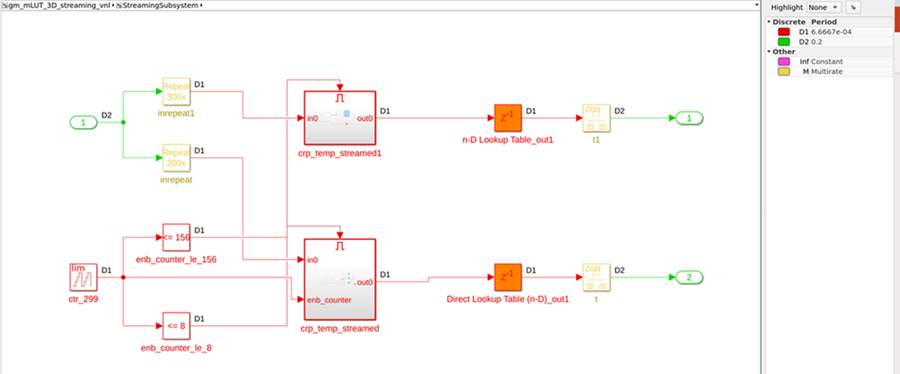

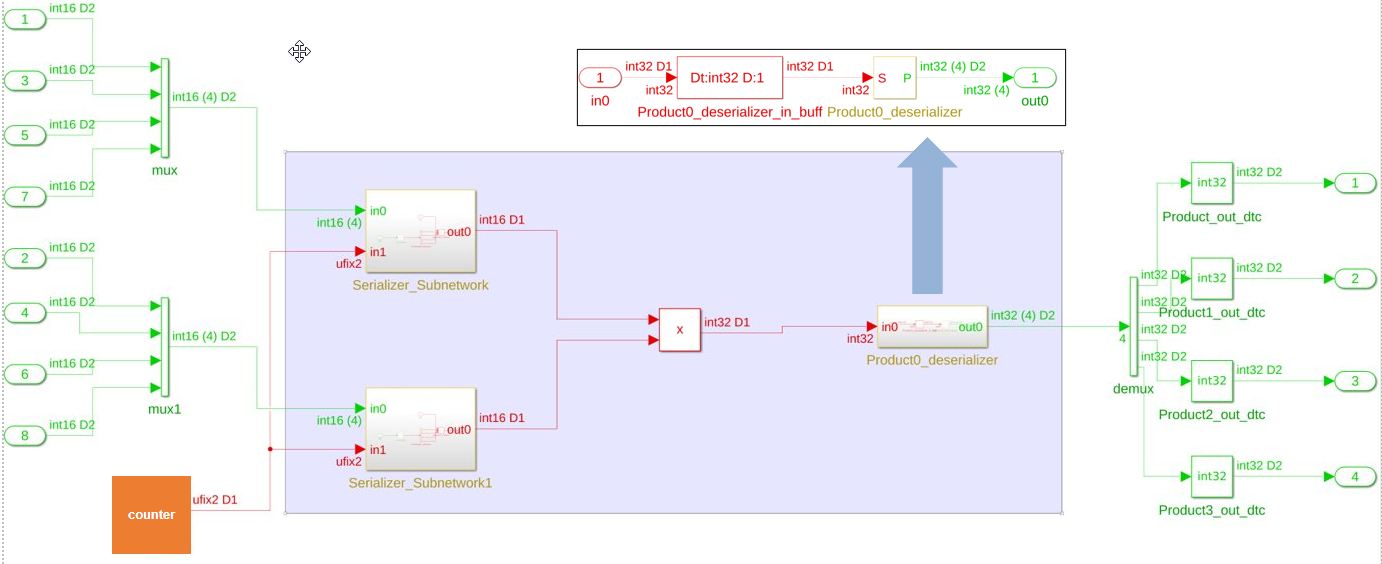

Enable sharing, streaming, and clock-rate pipelining optimizations concurrently

Prior to R2025a, if you enabled sharing, streaming, and clock-rate pipelining optimizations, the generated code applied only the optimizations for streaming and clock-rate pipelining. Starting in R2025a, the code generator concurrently applies the sharing, streaming, and clock-rate pipelining optimizations.

For more information on enabling optimizations, see Speed and Area Optimizations in HDL Coder.

In R2025a, HDL code you generate may have increased applications of optimization compared to previous releases.

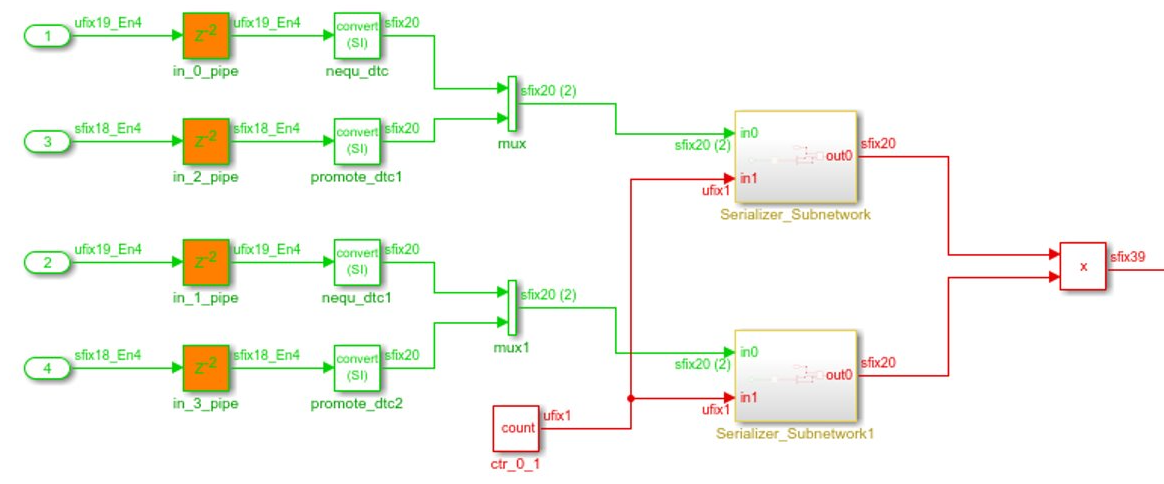

Use streaming optimization for complex data type inputs

When you use the streaming optimization for complex data type inputs, the optimized model uses

fewer resources than in previous releases. When you set the StreamingFactor HDL block property to a value greater than or equal to twice the input

size, HDL Coder applies the streaming optimization to complex inputs. Previously, HDL Coder allocated resources separately for the real and imaginary components which

results in the generated code consuming approximately twice the resources as the generated

code in R2025a. In R2025a, both real and imaginary parts share the same resource requiring

fewer resources.

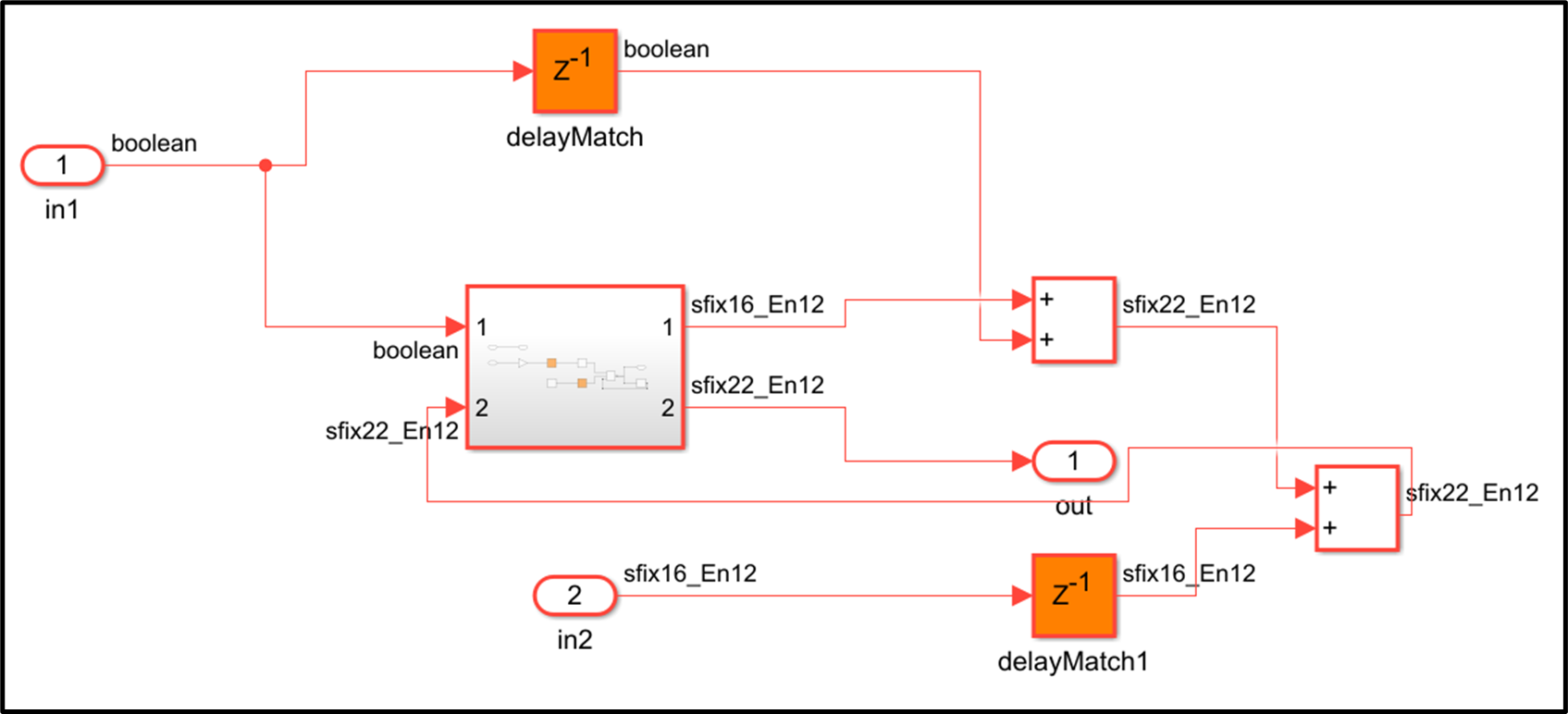

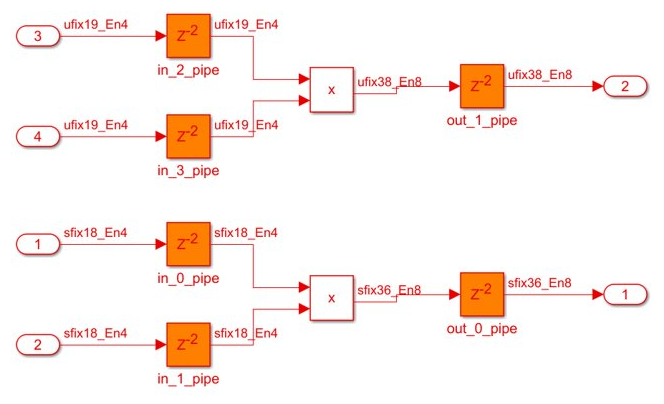

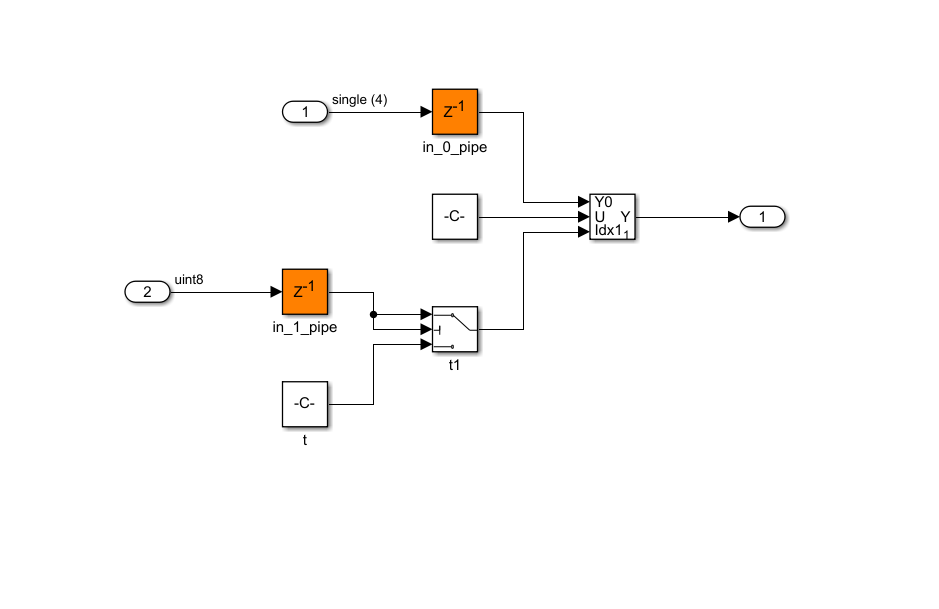

For example, before R2025a if a model has a Gain block that operates on complex data, the generated model contains two Gain blocks. For example, this image compares a model that uses the streaming optimization in R2025a and R2024b. The Simulink model contains a Gain block that uses complex data. In R2024b, the generated model contains two multiplier blocks. In R2025a, the generated model contains one multiplier block, which results in reduced resource usage.

Additionally, HDL Coder now supports these streaming operations for complex data types:

Complex data type inputs to a real-value Gain block

Complex data type inputs to a real-value Sum block

Real-value inputs to a complex data type Gain block

Real-value inputs to a complex data type Sum block

Addition of complex data types

I/O Optimizations

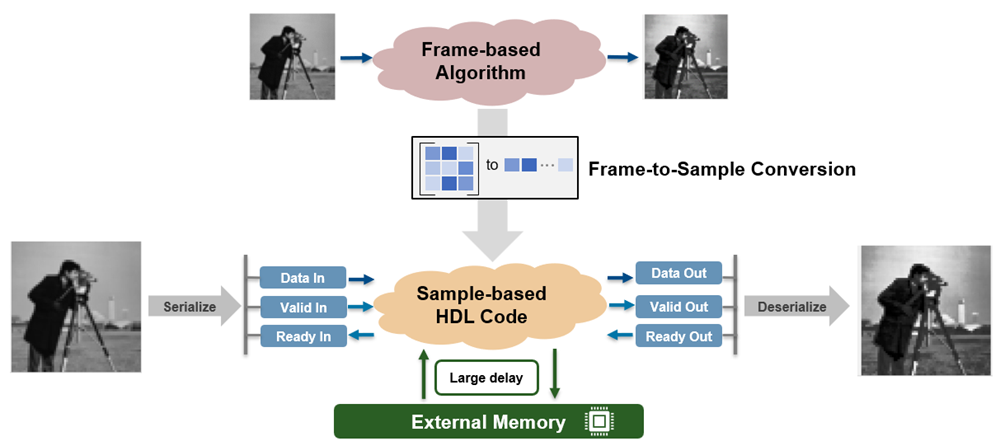

Improved external memory behavior for frame-to-samples optimizations in the case of multiple samples per cycle or 3-D frames

Prior to R2025a, for models with multiple samples per cycle or 3-D frames, HDL Coder created multiple unrelated external memories for the scalar values of each sample, equal to the samples per cycle multiplied by the frame depth.

Starting in R2025a, HDL Coder creates one external memory that stores a vector or matrix value on each cycle. This external memory does not reduce the total amount of storage, but it does reduce synchronization logic.

High-Level Synthesis Code Generation

Generate HLS IP Core with AXI4 Lite and external interfaces

In R2025a, you can generate a custom IP Core from a high-level design using HDL Coder. Further, you can deploy and run the custom IP core on all the AMD platforms.

To generate code using the IP Core workflow:

Setup the

Xilinx Vitis HLStool path by usinghdlsetuphlstoolpath(R2025a).Use the HDL Workflow Advisor to set the Set Target Interface task to map each input and output in the MATLAB design function to AXI4-Lite or external interfaces of the IP Core target.

Integrate the generated IP Core with Xilinx Vivado environment by using the Embedded System Integration task.

For more information, see Get Started with HLS IP Core Generation Workflow (R2025a).

Generate HLS code for MATLAB handle classes, value classes, and system objects

In R2025a, you can generate HLS code from MATLAB handle classes, value classes, and System object™. For more information, see MATLAB Classes (R2025a).

Functionality being removed or changed

Cadence Stratus renamed to Cadence Stratus HLS

Behavior change

In MATLAB to HLS code generation, the third-party HLS tool Cadence Stratus is renamed to Cadence Stratus HLS.

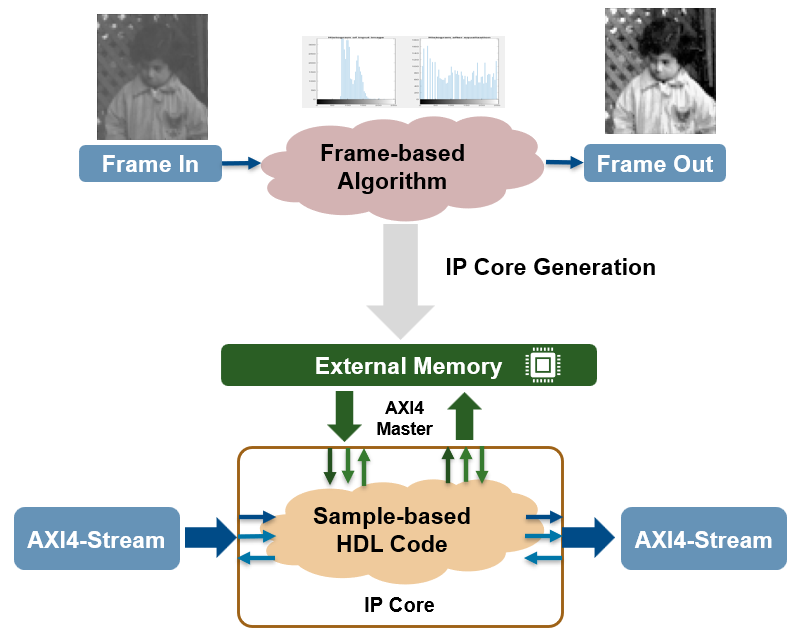

IP Core Generation and Hardware Deployment

Use multiple samples per cycle to enhance throughput in frame-to-sample IP core generation

Starting in R2025a, when you use AXI4 Stream interfaces, you can specify a value greater than one for the Samples per cycle model configuration parameter. HDL Coder packs the specified number of samples per cycle together and streams them in a single clock cycle when you use AXI4-Stream interfaces. For more information see, Stream Multiple Samples per Cycle.

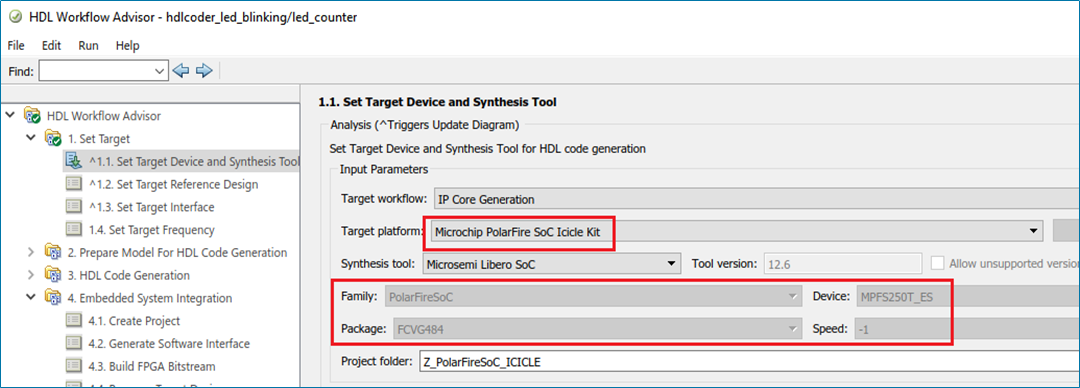

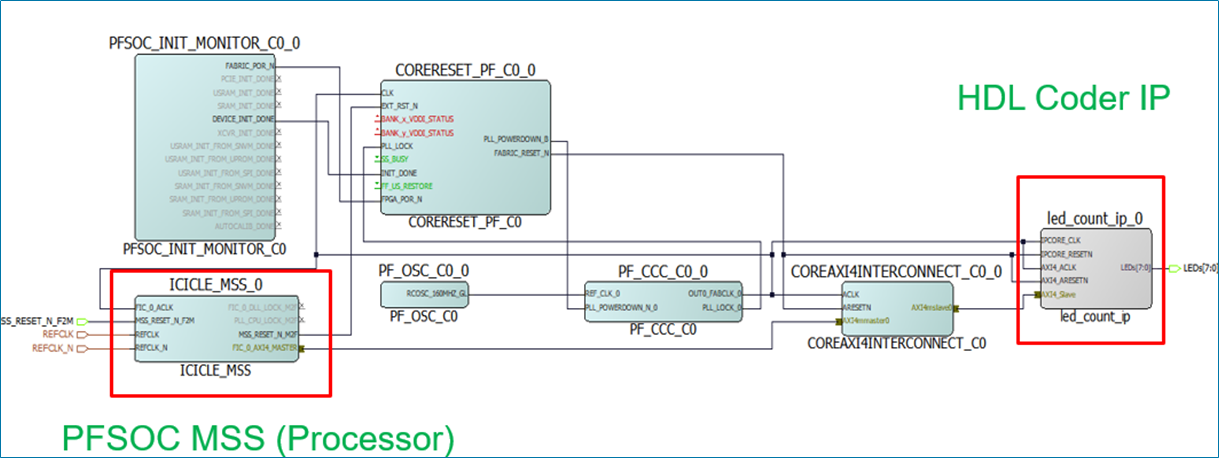

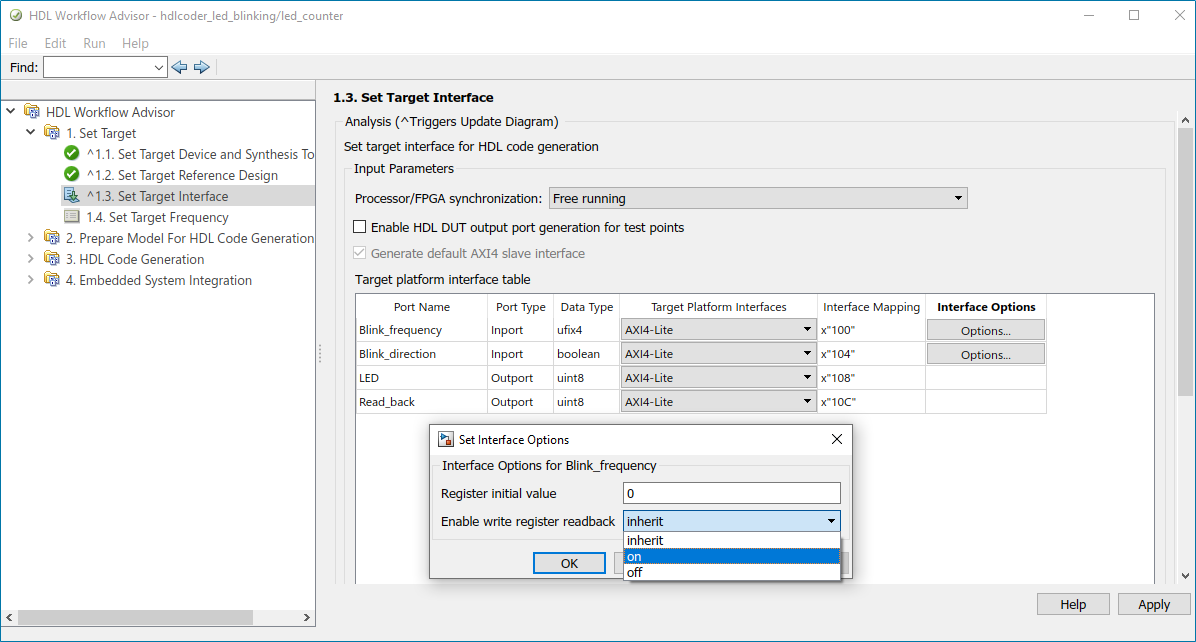

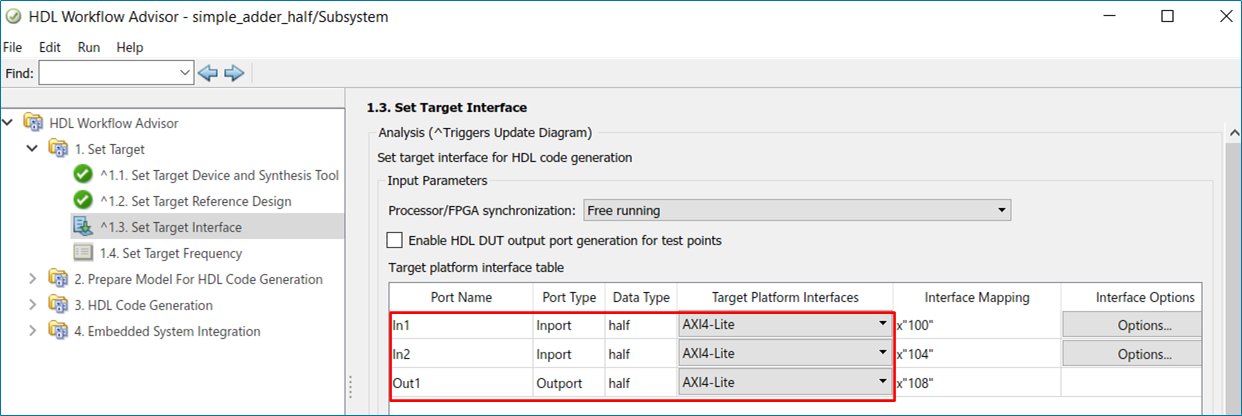

Download Linux images and generate host interface scripts for Microchip devices

When targeting Microchip FPGA and SoC devices, you can:

Generate a host interface script when generating an IP core, which enables you to use the MATLAB FPGA I/O functions,

readPortandwritePort, to read from and write to the AXI registers. For more information, see Get Started with IP Core Generation for Microchip PolarFire SoC Devices.Download a Linux image for the Polarfire® SoC Icicle Kit to boot your Microchip device from the SD card. Guided Hardware Setup for Microchip Boards

Unified hardware setup for HDL Coder supported hardware

You can now configure your hardware boards with the Hardware Setup tool, which operates

independently of vendor-specific HDL Coder support packages. Use the hdlHardwareSetup function to launch the Hardware Setup tool directly from

the MATLAB command window.

You can now use the Hardware setup tool to select the desired FPGA vendor and hardware

board, configure your hardware, download third-party tools, establish Ethernet connection,

and write the firmware image. In the Select a Hardware

Board step of the Hardware Setup tool, you can specify your FPGA vendor as

AMD, Intel or

Microchip, and then select the desired hardware boards from

the list. See Guided Hardware Setup for AMD Boards.

HDL Coder Support Package for Xilinx FPGA and SoC Devices renamed to HDL Coder Support Package for AMD FPGA and SoC Devices

The HDL Coder Support Package for Xilinx® FPGA and SoC Devices is now the HDL Coder Support Package for AMD FPGA and SoC Devices. To download the support package, see Download and Install HDL Coder Support Package for AMD FPGA and SoC Devices.

For more information on supported hardware, see AMD FPGA and SoC Devices.

Upgrade to Intel Quartus Prime Standard 23.1

HDL Coder now supports Intel

Quartus® Prime Standard 23.1. You can set up this third-party synthesis tool by using

hdlsetuptoolpath function and target

devices that are supported with that tool.

For more information about supported synthesis tools, see HDL Language Support and Supported Third-Party Tools and Hardware.

Upgrade to Xilinx Vivado 2024.1

HDL Coder now supports Xilinx

Vivado 2024.1. You can set up this third-party synthesis tool by using hdlsetuptoolpath function and target devices that are supported with that

tool.

For more information about supported synthesis tools, see HDL Language Support and Supported Third-Party Tools and Hardware.

Upgrade to Microchip Libero SoC 2024.1

HDL Coder now supports Microchip

Libero® SoC 2024.1. You can set up this third-party synthesis tool by using hdlsetuptoolpath function and target devices that are supported with that

tool.

For more information about supported synthesis tools, see HDL Language Support and Supported Third-Party Tools and Hardware.

Perform back-annotation analysis when you use the Intel Quartus Pro synthesis tool

Starting in R2025a, you can perform back-annotation analysis when you use the Intel Quartus Pro as the synthesis tool. Back-annotation helps you to identify critical paths in your model. To perform this analysis in the HDL Workflow Advisor, follow these steps:

In task 1.1. Set target Device and Synthesis Tool, set the Synthesis tool to

Intel Quartus Pro.Complete all the tasks until task 4.2.3. Perform Place and Route.

In task 4.3. Annotate Model with Synthesis Result:

Set Critical path source to

pre-routeorpost-route.Set Critical path number to

1or2or3.Set Chose Model to Annotate to

original.Select one or more options from Show all paths, Show unique path, Show delay data, and Show ends only to visually highlight one or more critical paths in your model.

For more information, see Annotate Model with Synthesis Result.

Use enable-based multicycle path constraints to meet timing requirements with Cadence Genus

Starting in R2025a, you can enable multicycle path constraints on your model when you

generate code for generic ASIC/FPGA devices using Cadence Genus synthesis tool. To enable multicycle path constraints, enable the Enable-based constraints model configuration

parameter and set the Target workflow parameter to Generic

ASIC/FPGA and Synthesis tool parameter to

Cadence Genus in the HDL Workflow Advisor. The HDL Workflow Advisor

integrates these constraints into the synthesis TCL file, which reduces synthesis time by

relaxing the timing requirements on the synthesis tool. This approach helps achieve higher clock

rates and improves the timing of Simulink models that have multiple sample rates or that have speed and area optimizations

that insert pipeline registers. For more information, see Iteratively Meet Timing Requirements Using Multicycle Path Constraints for Cadence Genus.

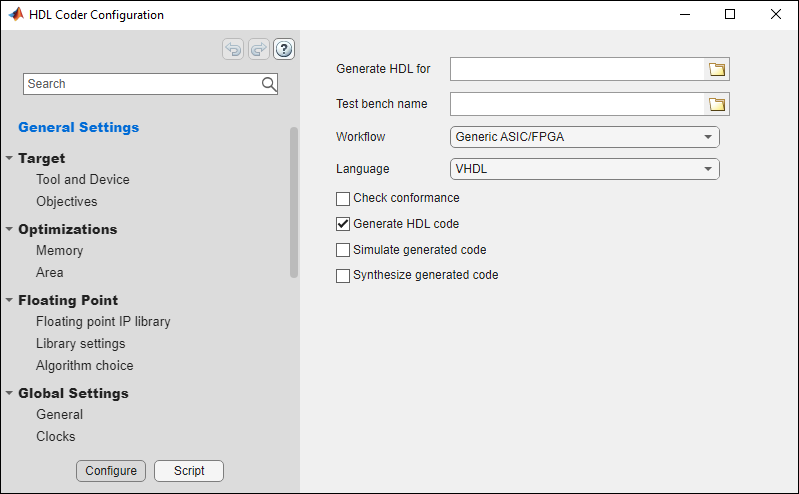

Generate Synopsys SpyGlass Lint report using HDL Workflow Advisor

Starting in R2025a, you can use the Synopsys SpyGlass Lint tool to perform RTL lint checks on the generated HDL code within the generic ASIC/FPGA workflow. To generate a lint report using the HDL Workflow Advisor, do this:

In the 1.1. Set Target Device and Synthesis Tool task, set Target workflow to

Generic ASIC/FPGA.Complete tasks up to 3.1. Set HDL Options.

In the 3.2. Generate RTL Code and Testbench task, select the Generate RTL code and Generate RTL lint check report options.

In the 3.3. Generate RTL Lint Check Report task:

Set the Lint tool to

Synopsys SpyGlass. This action populates the latest tool version for the SpyGlass Lint tool available on the MATLAB path.To use a custom lint file, enter the its name in the Custom lint file box or use the Add custom lint file button. Then, click Run This Task.

View the generated SpyGlass lint script and report files in the Result pane.

For more information, see Generate RTL Lint Check Report Using HDL Workflow Advisor and Synopsys SpyGlass Lint Tool.

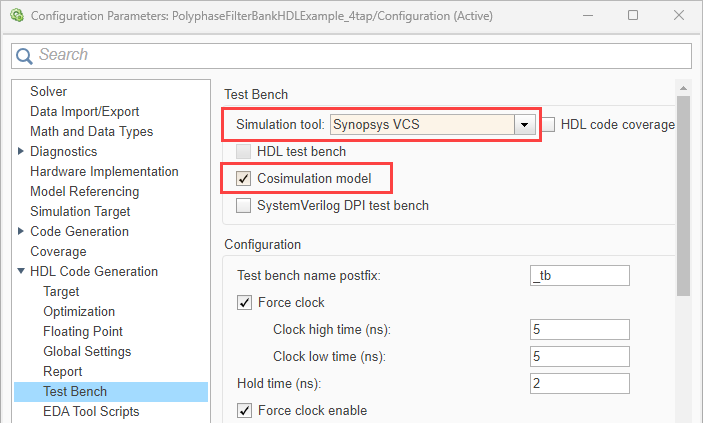

Generate cosimulation testbench for Synopsys VCS

When you perform HDL cosimulation using HDL Coder workflows, you now have the option to select the Synopsys® VCS® simulator to cosimulate the generated HDL.

You can use this feature with Simulink in these scenarios:

When using the

makehdltbfunction to generate a testbench, set theGenerateCosimModelproperty toVCS. For example:makehdltb("hdl_cosim_demo1/MAC",targetlang="vhdl",GenerateCosimModel="VCS")When using the Simulink HDL Workflow Advisor, open the configuration parameters for your model, and on the left pane, expand HDL Code Generation and select Test Bench. Then set Simulation tool to

Synopsys VCS.

You can use this feature with MATLAB in this scenario:

When using the

coder.HdlConfigobject, set theCosimToolproperty toVCS. For example:hdlcfg = coder.config("hdl"); % Create a default "hdl" config hdlcfg.CosimTool = "VCS";

For more information, see Generate Cosimulation Model.

This feature requires an HDL Verifier™ license.

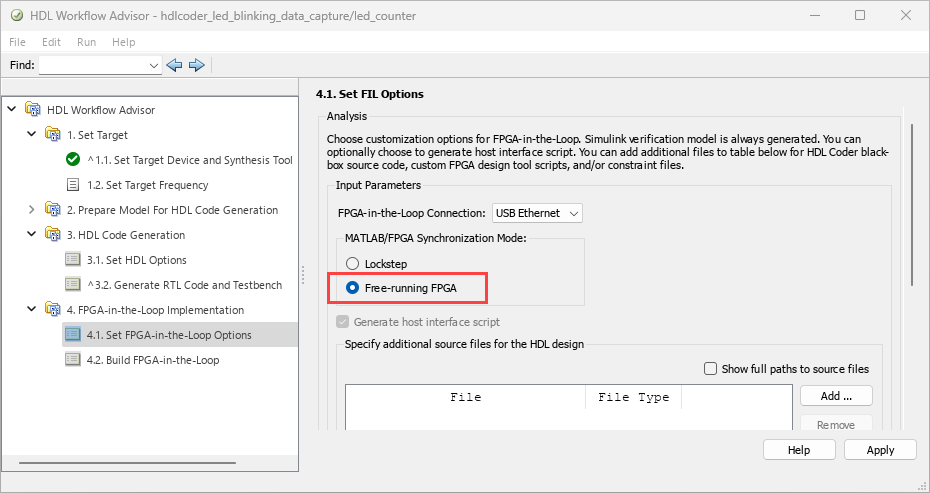

Stream data in free-running mode using FPGA-in-the-loop workflow

FPGA-in-the-loop in HDL Workflow Advisor supports free-running mode for streaming data between MATLAB and a DUT executing on an FPGA. This mode adds the option for the DUT to operate asynchronously with MATLAB.

To use this mode, in HDL Workflow Advisor, in the 4.1. Set FPGA-in-the-Loop Options step, under MATLAB/FPGA Synchronization mode, select Free-running FPGA.

The feature is supported on these SoC boards over an Ethernet or USB Ethernet interface:

ZedBoard™

AMD ZC702 Evaluation Kit

AMD ZC706 Evaluation Kit

AMD ZCU102 Evaluation Kit

AMD ZCU111 Evaluation Kit

AMD ZCU208 Evaluation Kit

AMD ZCU216 Evaluation Kit

AMD VCK190 Evaluation Kit

Intel Agilex® 7 SoC Development Kit (supported over Ethernet interface only)

Note

This feature works only when you use FIL with a MATLAB System object.

For more information, see Execute Free-Running FPGA-in-the-Loop Using HDL Workflow Advisor (HDL Verifier).

This feature requires an HDL Verifier license.

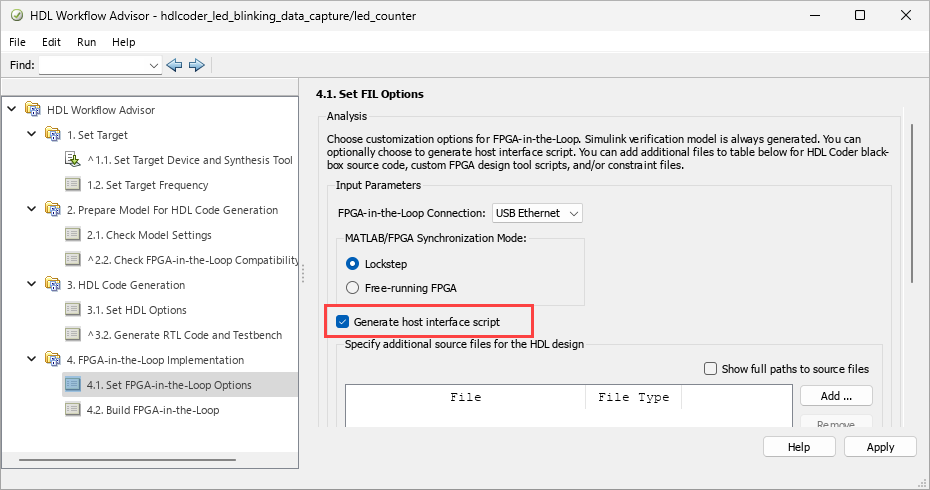

Generate host interface script for FPGA-in-the-loop workflow

You can now generate a host interface script, gs_<DUTName>_interface_fil.m, when you use FPGA-in-the-loop in HDL Workflow Advisor.

This script creates a filObj object for interfacing with your FPGA from MATLAB. The interface script contains MATLAB commands that connect to your hardware and program the FPGA, and examples of how to exchange data with your algorithm as it runs on hardware.

To generate a host interface script, in HDL Workflow Advisor, in the 4.1. Set FPGA-in-the-Loop Options step, select Generate host interface script. For free-running mode, this option is selected by default.

This feature requires an HDL Verifier license.

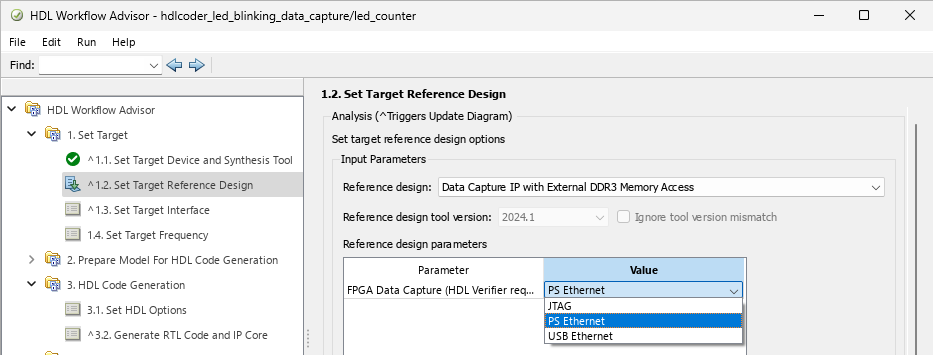

Capture data over PS Ethernet and USB Ethernet interfaces using FPGA data capture

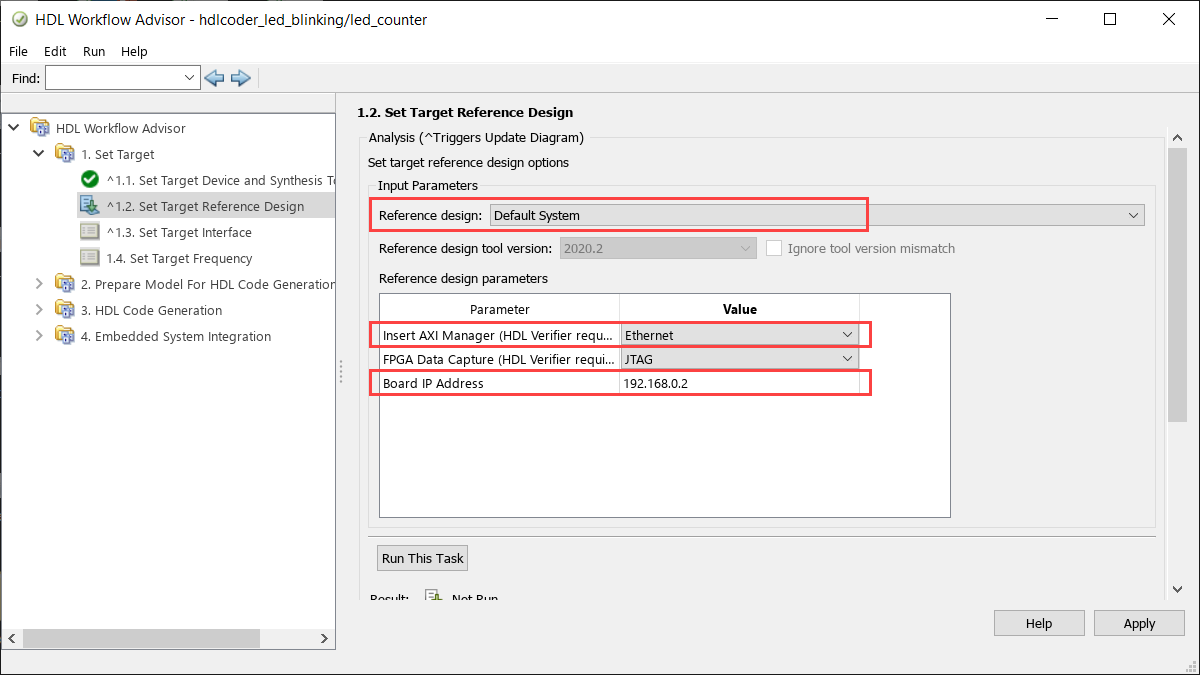

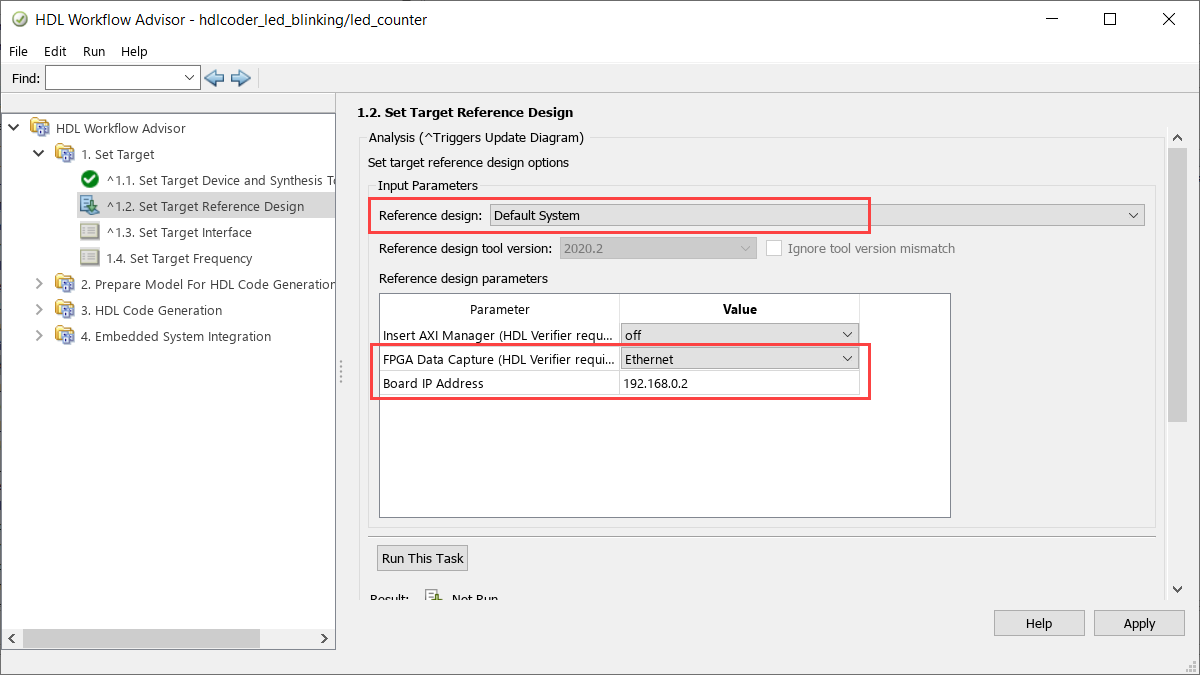

FPGA data capture in HDL Workflow Advisor now supports the PS Ethernet and USB Ethernet interfaces. To run FPGA data capture over a PS Ethernet interface, in the 1.2. Set Target Reference Design step, set FPGA Data Capture (HDL Verifier required) to PS Ethernet. To run FPGA data capture over a USB Ethernet interface, set FPGA Data Capture (HDL Verifier required) to USB Ethernet.

By default, the PS Ethernet and USB Ethernet options are available for these boards:

AMD ZCU102 Evaluation Kit (with the

Default system with data capture with external DDR4 memory accessreference design)AMD ZC706 Evaluation Kit (with the

Data Capture IP with External DDR3 Memory Accessreference design)ZedBoard (with the

Default systemreference design)

To enable these options for other boards, manually add the connection types in the

plugin_rd reference design definition file by using the addFPGADataCaptureInterface method before you start the HDL Workflow Advisor

tool.

You can enable PS Ethernet or USB Ethernet interface only when targeting these boards:

ZedBoard

AMD ZC702 Evaluation Kit

AMD ZC706 Evaluation Kit

AMD ZCU102 Evaluation Kit

AMD ZCU111 Evaluation Kit

AMD ZCU208 Evaluation Kit

AMD ZCU216 Evaluation Kit

For more detailed generation and data capture steps, see Data Capture Workflow (HDL Verifier).

This feature requires an HDL Verifier license.

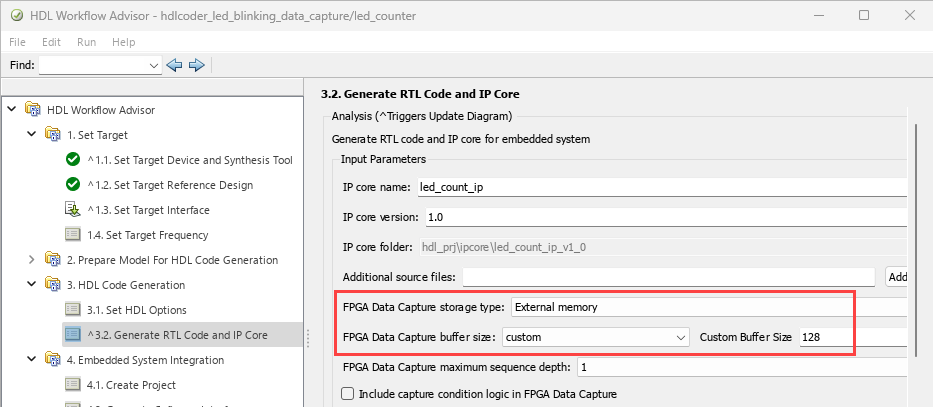

Use external DDR memory to capture large data using FPGA data capture

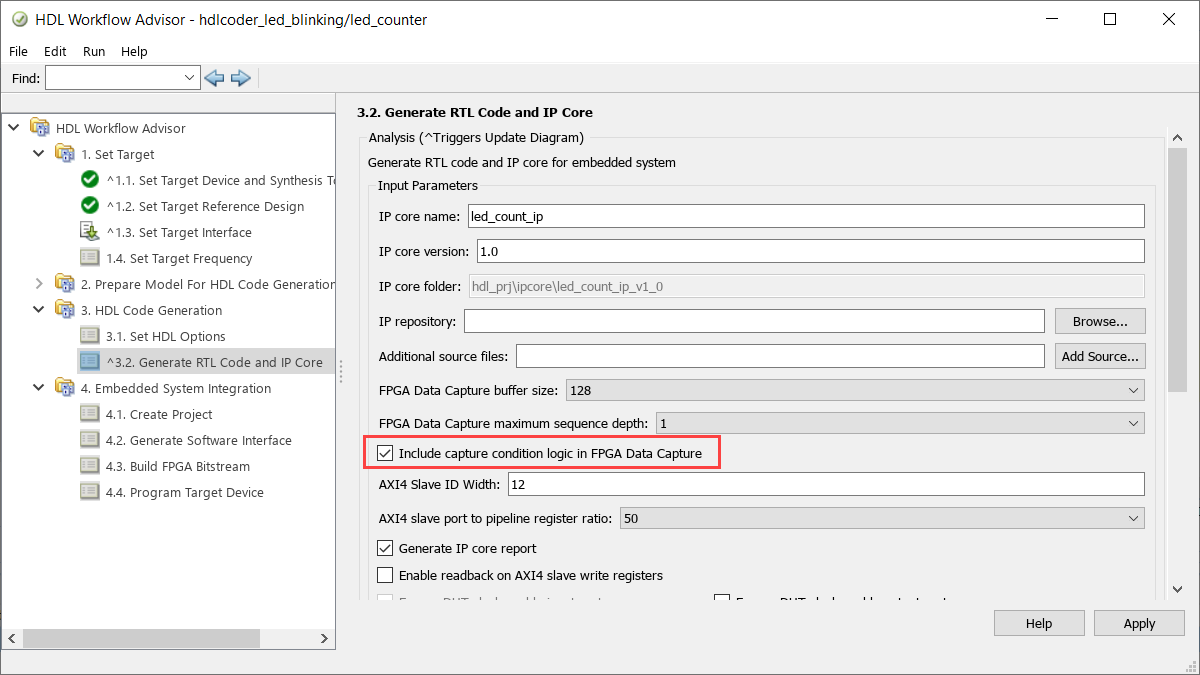

FPGA data capture in HDL Workflow Advisor now supports external DDR memory to capture up to two gigasamples of large data. To expand the memory size for capturing the data, in the 3.2. Generate RTL Code and IP Core step, set FPGA Data Capture storage type to External memory and FPGA Data Capture buffer size to custom. Then, specify Custom Buffer Size as the required value, in powers of 2, 2N, where N is an integer from 7 to 31.

By default, the External memory option is available for these boards:

AMD ZCU102 Evaluation Kit (with the

Default system with data capture with external DDR4 memory accessreference design)AMD ZC706 Evaluation Kit (with the

Data Capture IP with External DDR3 Memory Accessreference design).

To enable this option for other boards, configure the plugin_rd

reference design definition file by using the addFPGADataCaptureInterface method before you start the HDL Workflow Advisor

tool.

Note

You can enable external memory only when targeting the AMD devices over a JTAG, PS Ethernet, or USB Ethernet interface.

For an example, see Debug IP Core Using FPGA Data Capture. For more detailed generation and data capture steps, see Data Capture Workflow (HDL Verifier).

This feature requires an HDL Verifier license.

Use AXI4 Master interface with an address width greater than 32 bits in reference designs

Starting in R2025a, you can use an AXI4 Master interface with an address width greater than

32 bits. This change allows the AXI4 Master interface on your IP core to access memory locations

with base addresses beyond the 32-bit (4 GB) range. You can define the address width for your

AXI4 Master interface in user-defined reference designs. For more information, see addAXI4MasterInterface.

Use reference design to access external LPDDR4 memory on Xilinx Versal AI core series VCK190 evaluation kit

You can now use the Default system with External LPDDR4 Memory Access reference design for the Xilinx Versal® AI core series VCK190 evaluation kit. Use this reference design to access external memory on Versal devices from your HDL Coder generated IP core.

For more information about this reference design, see Perform Large Matrix Operations Using External Memory.

Unmapped ports are not automatically assigned when switching synchronization modes

Starting in R2025a, in the HDL Workflow Advisor, when you set Processor/FPGA synchronization mode to Coprocessing -

blocking, HDL Coder no longer assigns unmapped ports to the default bus interface. You must

manually assign the unmapped ports.

If you use the

Coprocessing - blocking setting in a model prior to R2025a, do no

explicitly map the ports, and generate an IP core, the IP core you generate in R2025a may be

different than a core generated in earlier releases. You must explicitly map the ports to

the default bus interface before running IP core generation.

Generate HDL code and perform synthesis using Cadence Genus on ASIC devices

The Generate HDL Code and Perform Synthesis Using Cadence Genus on ASIC Devices example shows how to generate and synthesize HDL code for generic ASIC devices using the HDL Workflow Advisor and the Cadence Genus synthesis tool. This example guides you on how to use either the default synthesis settings or your own custom synthesis settings. For more information, see Generate HDL Code and Perform Synthesis Using Cadence Genus on ASIC Devices.

Generate host interface script for IP cores in MATLAB-to-HDL workflow

You can now generate a host interface and a setup script when you generate an IP core in the MATLAB-to-HDL Workflow Advisor.

To generate a host interface script in the Workflow Advisor, under the Embedded System Integration task, right-click the Generate Software Interface subtask and select Run This Task.

This subtask generates the interface script gs_<modelName>_interface.m

and the setup script gs_<modelName>_setup.m. These scripts set up and

interface with the generated and deployed IP core. You can use these scripts to perform read and

write operations to the AXI-accessible registers or transfer frames of data to IP core through

the DMA and AXI-4 Stream interface. For more information, see Get Started with IP Core Generation from MATLAB Function.

Real-Time Hardware Deployment

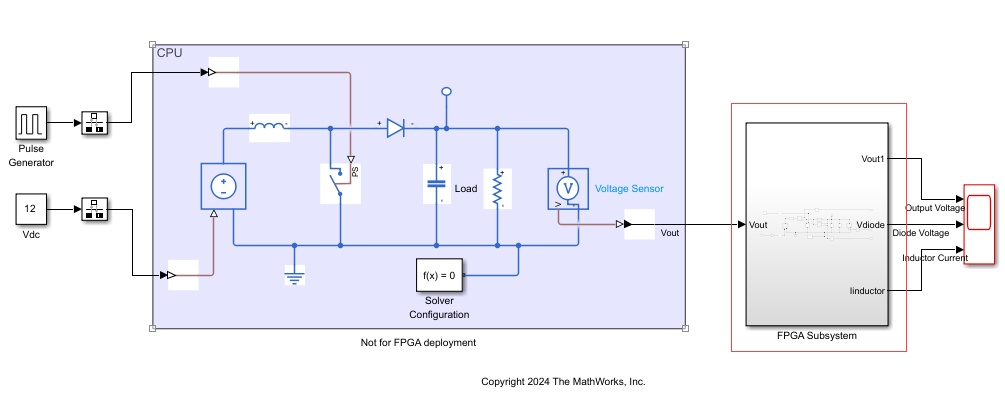

Simscape hardware-in-the-loop workflow: Reference applications

Real-Time Simulation of Modular Multilevel Converter for FPGA Deployment (R2025a)

This example shows how to model a modular multilevel converter (MMC) with half-bridge power modules by using generic switching function modeling approach, where the number of power modules is highly scalable. This example uses a hybrid plant model containing Simulink and Simscape™ blocks. You can generate HDL code and deploy onto a target hardware.

Enhancements to automatic replacement of Simscape components with optimized equivalents for FPGA deployment

Replacement of Simscape switches and converter blocks with their dynamic equivalents:

In a generated optimized model, gate ports of the replaced blocks now automatically connect to their respective sources. This enhancement supports scalar signals and gate inports that are directly connected to Simulink-PS Converter (R2025a) (Simscape) block.

Before R2025a, in the generated optimized model, you had to manually connect any gate signal inports of the replaced blocks to their respective sources and remove any additional Simulink-PS Converter (R2025a) (Simscape) blocks. For more information on replacing switches and converter blocks with their dynamic equivalents, see

sschdl.generateOptimizedModel(R2025a).Replacement of Simscape components with optimized equivalents:

On replacement of the Simscape PMSM (R2025a) (Simscape Electrical) block with an equivalent optimized PMSM block, the Simscape network splits and a secondary Solver Configuration (R2025a) (Simscape) block is now automatically added and connected. The

sschdl.generateOptimizedModelfunction automatically sets initial conditions for the optimized PMSM block based on the original Simscape model. You can tune the run-time parameters in the model and rerun thesschdl.generateOptimizedModelfunction to generate optimized PMSM block with updated initial conditions.Previously, when the Simscape network split, you had to connect a Solver Configuration block to the disconnected segment of the network manually and the optimized PMSM block was generated with the initial conditions computed for the original Simscape model. For more information, see Optimize Simscape Three-Phase PMSM Drive Model for Efficient HDL Code Generation and Synthesis (R2025a).

Improved FPGA bitstream generation from Simscape models with tunable run-time parameter values

The parameter tuning now supports linear time-invariant models with local solver set

to Trapezoidal Rule. You can modify the run-time parameter

values in the generated FPGA bitstream for your Simscape models and fine-tune any run-time configurable parameter values in the

generated FPGA bitstream without the need to rerun the synthesis for the generated HDL

implementation models. For more information, see sschdl.updateRuntimeParameters (R2025a).

Previously, you could tune Simscape run-time parameters only for Simscape models with

local solver set to Backward Euler.

Improved fixed-point data type support for nonlinear Simscape models

The Simscape hardware-in-the-loop (HIL) workflow now provides improved support for nonlinear Simscape models with fixed-point data type by using lookup table approximation. With this enhancement, you can achieve better timing and resource utilization for nonlinear Simscape models containing Trigonometric Function (R2025a) blocks . For more information about how to decide on using fixed-point data types for your plant models, see Use Fixed-Point Precision (R2025a).

HDL Code generation for Sine Wave block

The Simscape hardware-in-the-loop (HIL) workflow now supports HDL code generation for the Sine Wave (R2025a) block.

Model and Architecture Design

Generate HDL code for Bus elements with matrix type

You can now generate HDL code for Subsystem blocks that contain Bus Creator (R2024b), Bus Selector (R2024b), Bus Assignment (R2024b), In Bus Element (R2024b), or Out Bus Element (R2024b) blocks that use matrix type elements.

For more information, see Signal and Data Type Support (R2024b).

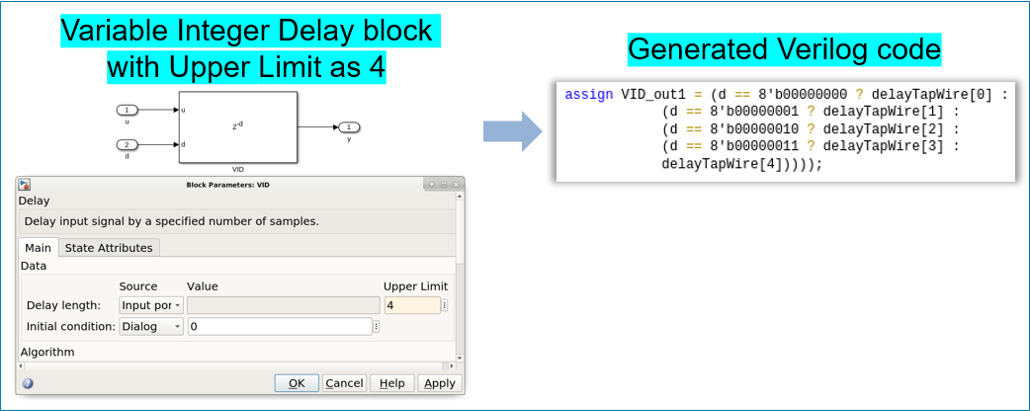

Use structures as initial values for Delay blocks

You can now generate HDL code for Delay (R2024b) blocks that use structures to specify the initial conditions. You also use structures as the initial values in other delay blocks, including the Unit Delay (R2024b), and Tapped Delay (R2024b) blocks. Using this enhancement, when you use bus input for a Delay block, you can set initial condition for the delay block with a structure value to initialize the bus delay.

To generate HDL code for a Delay block using initial conditions defined by structures:

Define a structure variable in the model workspace, MATLAB base workspace, mask workspace, or Simulink data dictionary.

Assign the initial condition value to this structure variable.

In the Block Parameters dialog for the Delay block, set the Initial Condition parameter to

Dialogand input the structure variable in the Value field.Generate the HDL code for your model.

For more information, see HDL Code Generation (R2024b).

Use virtual buses as inputs to resettable Delay blocks

You can now generate HDL code for Delay (R2024b) blocks that include an external reset port and that uses a virtual bus as an input. Using this enhancement, you can generate HDL code for these delay blocks that uses virtual bus as input:

Resettable Delay

Enabled Resettable Delay

Tapped Delay Resettable Synchronous

Tapped Delay Enabled Resettable Synchronous

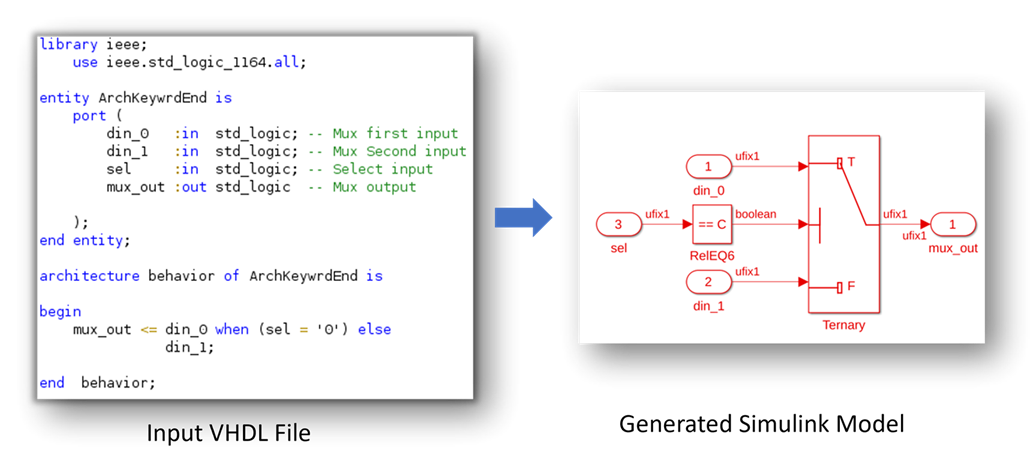

Import VHDL code into the Simulink environment using importhdl

function

You can now import synthesizable VHDL code into the Simulink modeling environment. When you execute the importhdl (R2024b) function, the function analyzes the VHDL files and generates a corresponding Simulink model. This model visually interprets the VHDL code, showcases its functionality and behavior.

When you import the VHDL code, make sure that the constructs used in the HDL code are

supported by importhdl function. For more information, see Supported VHDL Constructs When Generating Simulink Models from VHDL Code (R2024b).

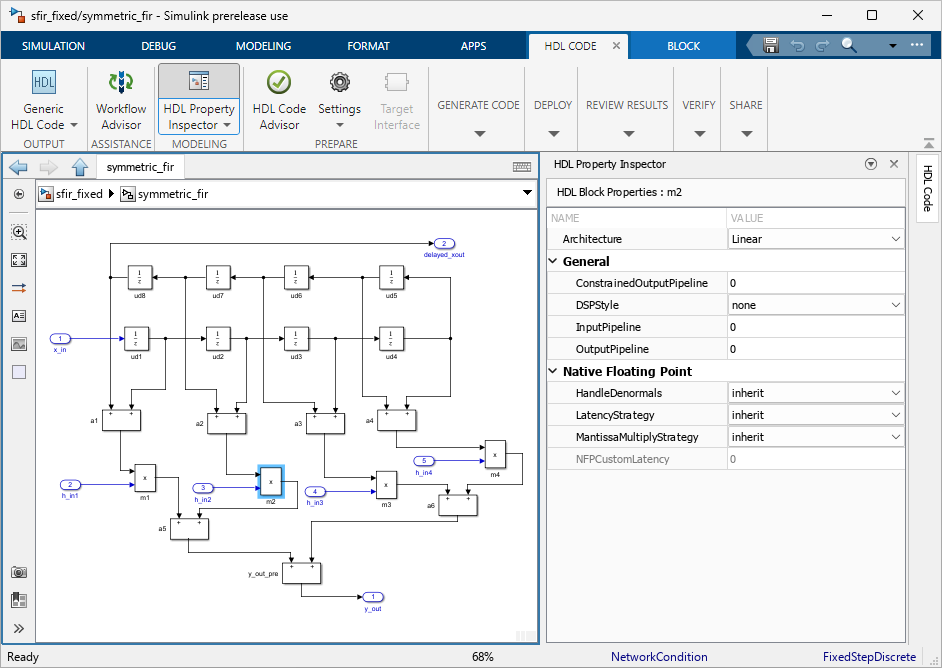

Use HDL Property Inspector to edit HDL Block Properties

You can now edit the HDL block properties of a block or a subsystem by using HDL Property Inspector pane. When you use the HDL Property Inspector pane, you can set the HDL Properties as you work. The values take effect when you set them. For more information, see Set and View HDL Model and Block Parameters (R2024b).

To open the HDL Property Inspector pane from the Simulink Toolstrip, first open the HDL Coder app from the Apps menu. In the HDL Code tab, click HDL Property Inspector.

In the HDL Property Inspector, you can assign values to HDL block properties using the variables declared in MATLAB base workspace, mask workspace, or model workspace.

Multi-index input arguments into cell arrays by using

varargin

You can now use varargin (R2024b) in a MATLAB

Function block that has the HDL block property

Architecture set to MATLAB Datapath

and multi-index input arguments into cell arrays. For example, you can now generate HDL

code for this code

snippet:

[x, y] = varargin{1:2};Use Signal Editor block to generate HDL test bench with multiple test cases

Starting in R2024b, you can generate test bench code that includes multiple test cases by using the Signal Editor block. You can configure the block with multiple active scenarios and each containing multiple signals. By modeling multiple simulations, you can improve the test coverage of the HDL code, while simultaneously reducing the time and effort required to evaluate and validate a complex system.

For more information, see Signal Editor (R2024b).

Block Enhancements

HDL code generation for Array Processing Subsystem block

You can now generate HDL code for the Array Processing Subsystem (R2024b) block. The Array Processing Subsystem block applies an algorithm to each element of an input matrix and is optimized for large input matrices such as image data. Use the Array Processing Subsystem for element-wise image processing tasks and other element-wise operations for large inputs.

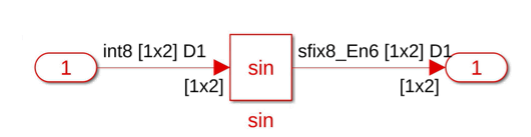

Generate HDL code for Trigonometric Function blocks that use the lookup table-based approximation method

You can now generate HDL code for the Trigonometric Function blocks

when the Approximation method parameter is set to

Lookup and the Function parameter is

set to sin, cos,

sincos, or cos + jsin.

For more information, see Trigonometric Function (R2024b).

Initialize RAM banks in RAM System blocks with unique initial values for vector data inputs

Prior to R2024b, RAM System blocks that use vector data inputs assume that the RAM banks are in parallel arrays and initialize these RAM banks with the same initial values.

Starting in R2024b, you can initialize RAM banks with unique initial values. To specify an initial value for the RAM System block, in the Block Parameters dialog box, enter a unique vector or matrix value for Initial output of RAM parameter.

You can initialize these RAM System blocks:

Single Port RAM System (R2024b)

Simple Dual Port RAM System (R2024b)

Dual Port RAM System (R2024b)

True Dual Port RAM System (R2024b)

Simple Tri Port RAM System (R2024b)

Write to RAM in columns of data using column-write operations in RAM System blocks

Starting in R2024b, you can use the column-write method to selectively modify specific parts of the memory without altering the remaining parts at a specified memory address. In this method, you conceptualize RAM as a collection of equally sized columns. During a write cycle, you can precisely control the writing process for each individual column. The data type and value of the write enable input, along with the data type of write data input, determine the width of each column and which columns you target for writing at the specified memory address.

You can use column-write with these RAM System blocks:

Single Port RAM System (R2024b)

Simple Dual Port RAM System (R2024b)

Dual Port RAM System (R2024b)

True Dual Port RAM System (R2024b)

Simple Tri Port RAM System (R2024b)

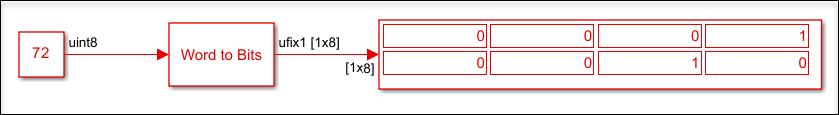

Choose the bit ordering for the Bits to Word or Word to Bits blocks as MSB or LSB first

You can now set the input bit order for the Bits to Word (R2024b) block to be the most significant bit (MSB) or least significant bit (LSB) first. You can select the bit order by using the Input bit order block parameter.

Similarly, you can choose the output bit order for the Word to Bits (R2024b) block. Select

the Output Bit order block parameter as MSB

first or LSB first.

In the Bits to Word block, you can also specify whether to consider the output as signed integer or unsigned integer. Use the Treat output integer as parameter to define the output signedness.

Generate HDL code for the Bit to Integer Converter and Integer to Bit Converter blocks

Generate a VHDL, Verilog®, or SystemVerilog code for Bit to Integer Converter (R2024b) and Integer to Bit Converter (R2024b) blocks. These blocks are available in the Logic and Bit Operations library in the HDL Coder library. Use these blocks to map input vector bits to vectors of integers, or to map vectors of integers to vector bits.

DSP System Toolbox (DST) Filter blocks participate in HDL optimizations

These DSP System Toolbox filter blocks now participate in HDL optimizations:

Biquad Filter (R2024b) (DSP System Toolbox)

Discrete FIR Filter (R2024b)

CIC Interpolation (R2024b) (DSP System Toolbox)

CIC Decimation (R2024b) (DSP System Toolbox)

FIR Interpolation (R2024b) (DSP System Toolbox)

FIR Decimation (R2024b) (DSP System Toolbox)

With this enhancement, you can now apply HDL optimizations like streaming, sharing, clock rate pipelining, and several other optimizations to these blocks to optimize your HDL code for area and speed.

All other architecture settings have been removed from the HDL block property

Architecture. These blocks now have their

Architecture property set to

HDLDataPath. These Architecture

settings have been removed from the Filter blocks:

| Block | Architecture Settings |

|---|---|

| Biquad Filter (R2024b) (DSP System Toolbox) |

|

| Discrete FIR Filter (R2024b) |

|

| CIC Interpolation (R2024b) (DSP System Toolbox) |

|

| CIC Decimation (R2024b) (DSP System Toolbox) |

|

| FIR Interpolation (R2024b) (DSP System Toolbox) |

|

| FIR Decimation (R2024b) (DSP System Toolbox) |

|

Use clock-rate pipelining with RAM System blocks

You can use a RAM System block inside a data rate feedback loop and use clock-rate pipelining optimization. This model design is helpful for applications that require programmable or tunable lookup tables without having to regenerate bitstreams.

You can use clock-rate pipelining optimization with these RAM System blocks:

Dual Port RAM System (R2024b)

Simple Dual Port RAM System (R2024b)

Single Port RAM System (R2024b)

True Dual Port RAM System (R2024b)

Simple Tri Port RAM System (R2024b)

These blocks have a new parameter, Model RAM with cycle of delay, that you can use to specify whether to model the RAM with one cycle of delay.

To enable this parameter, clear the Use asynchronous read feature in target hardware parameter.

Alternatively, you can use the hdl.RAM (R2024b)

System object to model delay in your simulation by specifying the new property

ModelRAMDelay:

hRAM = hdl.RAM("RAMType","Single port",... "ModelRAMDelay",true);

ModelRAMDelay

is true by default and is disabled when AsyncRead is true.For more information, see Getting Started with RAM and ROM in Simulink (R2024b).

Certain RAM blocks are not recommended

Starting in R2024b, the Dual Port RAM (R2024b), Simple Dual Port RAM (R2024b), and Single Port RAM (R2024b) blocks are not recommended. Instead, use the Dual Port RAM System (R2024b), Simple Dual Port RAM System (R2024b), and Single Port RAM System (R2024b) blocks, respectively.

The alternative blocks offer these additional features:

Use of asynchronous read feature in your target hardware

Specification of write output behaviour

Support for RAM banks

Support for modeling RAM by one cycle of delay

The Dual Port RAM, Simple Dual Port RAM, and Single Port RAM blocks will be removed in a future release.

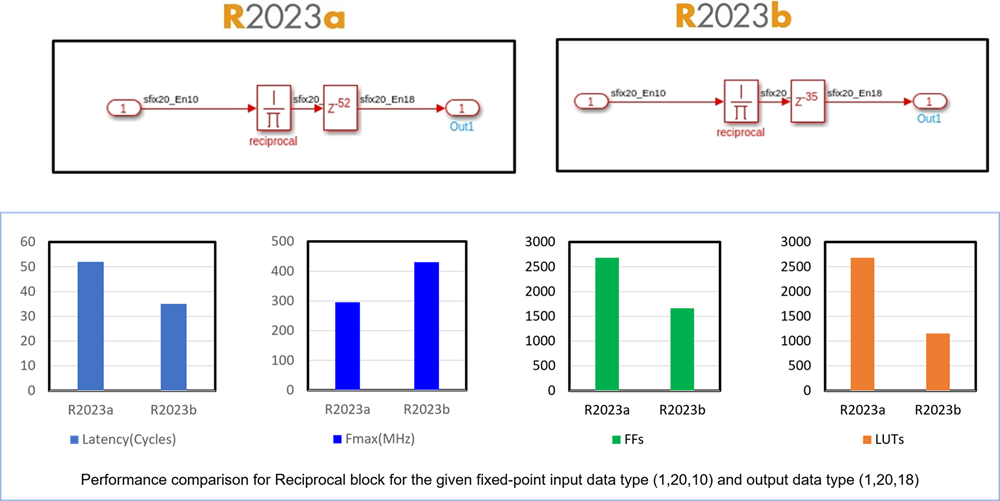

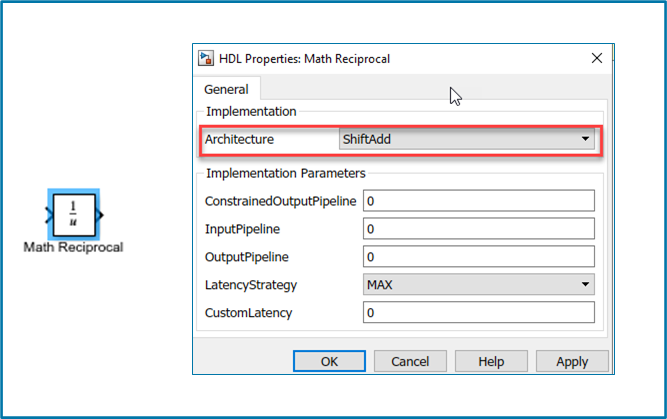

Default architecture for the Math Function Reciprocal block is

ShiftAdd

When you set the Function block parameter of a Math Function (R2024b) block to reciprocal, the default setting for the

Architecture HDL block property is now

ShiftAdd. The HDL code generated by the

ShiftAdd architecture is more hardware-friendly than that

produced by other existing architectures. Using this architecture, you can now generate

code for the block when it uses floating-point inputs.

The Architecture block property setting,

Math, has been removed from the Math Function block

when the Function block parameter is

reciprocal.

Functionality being removed or changed

"html" and "librarymodel" input arguments

of hdllib function are not recommended

Still runs

Starting R2024b, these syntaxes are not recommended for the hdllib (R2024b) function:

hdllib("html")hdllib("librarymodel")

These syntaxes will be removed in a future release.

To view blocks that are compatible with HDL code generation, use the

hdllib syntax

instead:

hdllib

Alternatively, in the Apps tab, select HDL Coder. In the HDL Code tab, select HDL Property Inspector > Open HDL Block Library.

Parameter name changes for RAM System blocks

Behavior change

Block parameters for these RAM System blocks have been renamed:

Single Port RAM System (R2024b)

Simple Dual Port RAM System (R2024b)

Dual Port RAM System (R2024b)

True Dual Port RAM System (R2024b)

Simple Tri Port RAM System (R2024b)

| Previous Name | Current Name |

|---|---|

| Specify the type of RAM | Type of RAM |

| Enable asynchronous reads | Use asynchronous read feature in target hardware |

| Specify the output data for a write operation | Behavior for write output |

| Specify the RAM initial value | Initial output of RAM |

Code Generation and Verification

Generate HDL code for fixed-point data types with word lengths greater than 128 bits

You can now generate HDL code for fixed-point data types with word lengths up to 65535 bits. Prior to R2024b, the maximum word length was 128 bits.

With this support, you can efficiently model wide data buses and larger integers without the complexity of piecing together smaller bits.

For more information, see Supported MATLAB Data Types, Operators, and Control Flow Statements (R2024b).

HDL code generation support for multidimensional interpolation

You can now generate HDL code for lookup tables by using the MATLAB function hdl.interpn (R2024b). The function supports multidimensional interpolation using

the specified method of approximation. You can generate synthesizable HDL code for this

function and deploy onto FPGAs and ASICs.

To enable this functionality, run the hdl.interpn function at the

MATLAB command prompt. For example:

hdl.interpn(X1,X2,...,Xn,V,Xq1,Xq2,...,Xqn,interpolation,extrapolation);

Here, X1,X2,...,Xn contain the coordinates of the sample points in

each dimension; V contains the corresponding function values at each

sample point; Xq1,Xq2,...,Xqn contain the coordinates of the query

point; and interpolation and extrapolation specify

the approximation methods.

For the hdl.interpn function, the approximation methods supported

for code generation are "linear" for interpolation

and "linear" and "nearest" for

extrapolation.

For more information, see hdl.interpn (R2024b).

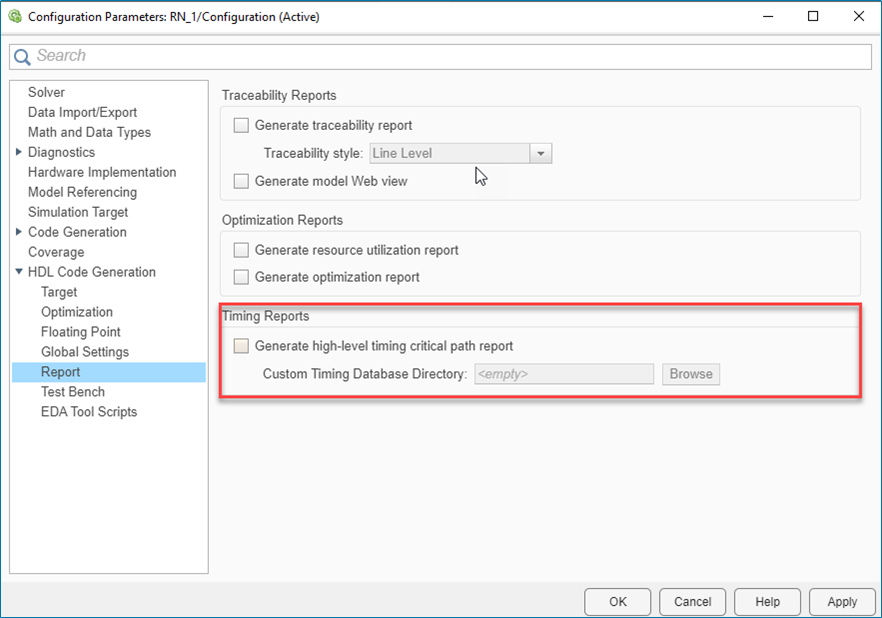

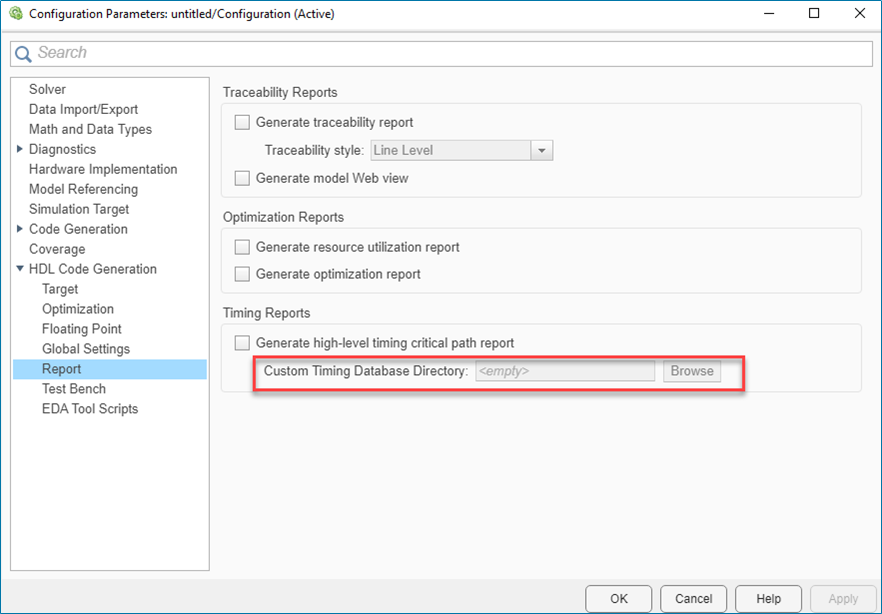

genhdltdb function: Generate timing databases for Cadence Genus and use technology library files as inputs

In R2024b, you can generate timing databases for Cadence Genus by using the genhdltdb (R2024b) function. Additionally, when using the

SynthesisDevicePart input argument, you can:

Pass technology library files

Pass the paths to the Cadence Genus tool and the technology library files as cell arrays

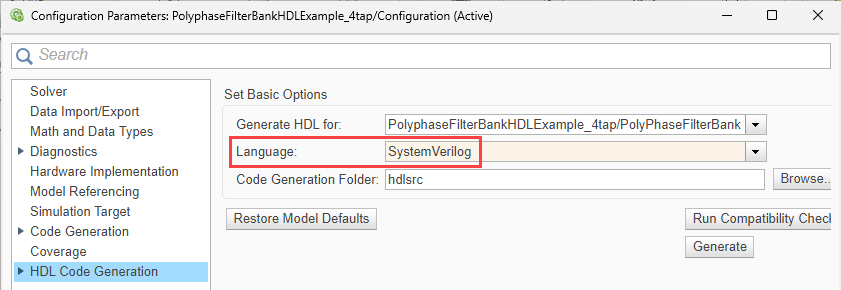

SystemVerilog DPI: Generate DPI testbench for SystemVerilog code generated from HDL Coder

You can now generate a DPI testbench for the SystemVerilog target language by using

the Configurations Parameters dialog box and/or makehdltb

function.

To generate a DPI testbench for the SystemVerilog code, follow these instructions:

Open the configuration parameters for your model.

On the left pane, select HDL Code Generation. Set Language to

SystemVerilog.

On the left pane, expand HDL Code Generation and select Test Bench. Select SystemVerilog DPI test bench.

Generate a DPI testbench by using the

makehdltb(R2024b) function. For example, use this command to generate the DPI testbench for thePolyphaseFilterBankHDLExample_4tap/PolyPhaseFilterBanksubsystem.makehdltb("PolyphaseFilterBankHDLExample_4tap/PolyPhaseFilterBank");

Alternatively, to perform steps 2 and 3, use the TargetLanguage (R2024b)

and GenerateSVDPITestBench (R2024b) arguments of the makehdltb

function, respectively. For example, use this command to set the target language to

SystemVerilog and generate the DPI testbench for the

PolyphaseFilterBankHDLExample_4tap/PolyPhaseFilterBank

subsystem.

makehdltb("PolyphaseFilterBankHDLExample_4tap/PolyPhaseFilterBank", ... "GenerateSVDPITestBench","Modelsim","TargetLanguage","SystemVerilog");

This feature requires an HDL Verifier license.

Speed and Area Optimizations

Enhancements to loop streaming

You can reduce area resources by using loop streaming to share the loop body. Starting in R2024b, you can stream loops:

Inside nested conditional loops

That have a loop increment value greater than one

That have a negative loop increment value

Additionally, you can use a System object in fully streamed loops. Starting in R2024b, you can use a System object in fully streamed loops that have no errors or warnings. For example, if you stream a loop with a factor that does not match the total number of loop iterations, you cannot use a System object in this loop. See Optimize MATLAB Loops (R2024b).

Leverage FPGA and SoC digital signal processing primitives usage in critical path estimation

Starting in R2024b, HDL Coder accounts for the FPGA and SoC digital signal processing primitive (DSP) resources during timing estimation, which results in an optimized timing database and critical path estimation report. You can use these methods and attributes to customize how HDL Coder synthesizes and accounts for DSPs in the timing report:

hasDSPs— Use this method to check if your device uses DSPs.countDSPs— Use this method to return the number of DSPs found during synthesis.dspSynthesisAttribute— Use this cell array attribute to force the multipliers to map to the DSPs.dontTouchSynthesisAttribute— Use this cell array attribute to not optimize signals that are connected to input and output pipeline registers during synthesis.

See Generate Custom Timing Database for Custom Tools and Devices (R2024b).

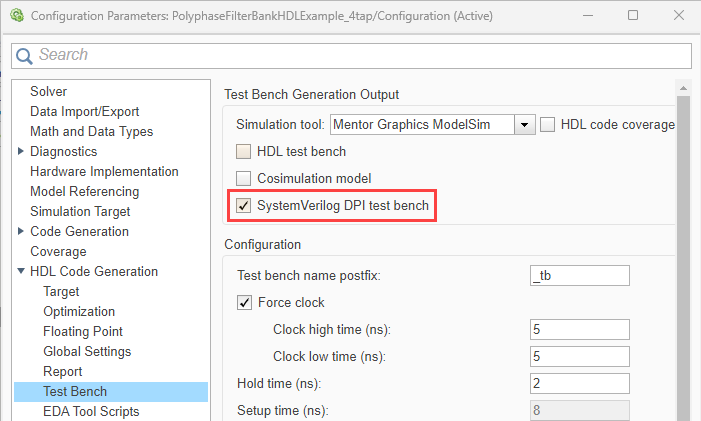

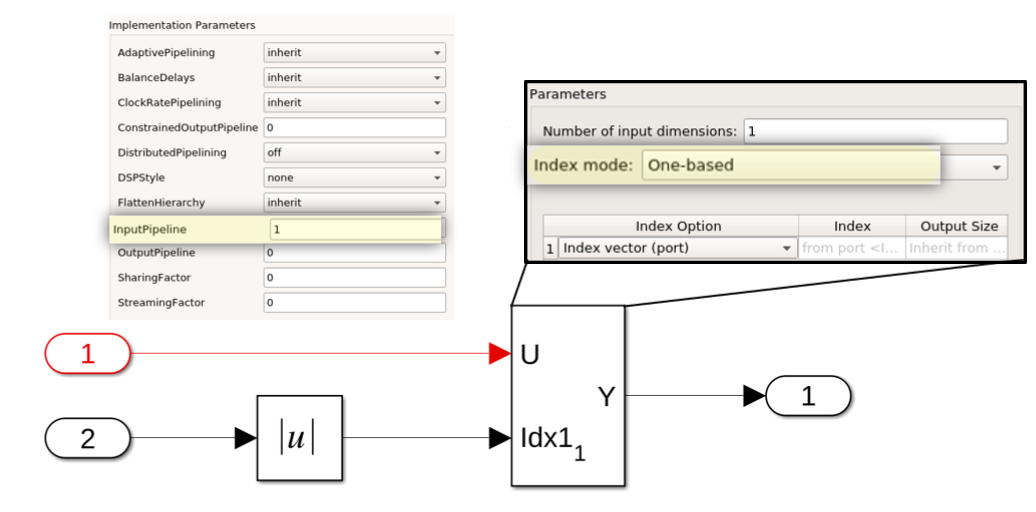

Use HDL optimizations for Stateflow blocks

You can now apply HDL optimizations to Stateflow blocks to enhance your HDL code in terms of speed and area. You can use optimizations for Chart (R2024b) (Stateflow) blocks that model Mealy charts or Classic charts, State Transition Table (R2024b) (Stateflow) blocks, Truth Table (R2024b) (Stateflow) blocks and Requirement Table blocks.

You can leverage these HDL optimizations:

Clock-Rate Pipelining (R2024b)

Delay Balancing (R2024b)

Resource Sharing (R2024b)

Adaptive Pipelining (R2024b)

Distributed Pipelining (R2024b)

Critical Path Estimation (R2024b)

InputPipeline (R2024b)

OutputPipeline (R2024b)

ConstrainedOutputPipeline (R2024b)

Additionally, you can use these optimizations for Classic charts and Mealy charts:

Constant Multiplier Optimization (R2024b)

GuardIndexVariables (R2024b)

InstantiateFunctions (R2024b)

LoopOptimization (R2024b)

Map Persistent Variables To RAM (R2024b)

HDL Pipeline Pragma (R2024b)

You can also observe the associated latency of the block in the generated model, which is indicated by the number of delays. For more information, see Introduction to Stateflow HDL Code Generation (R2024b).

Optimization report includes delay balancing information

When you generate code for a design under test (DUT), HDL Coder produces optimization reports. Starting in R2024b, the Delay Balancing optimization report contains a new section with detailed information on blocks that introduce latencies due to optimization requests or the implementation of certain block architectures.

For more information on delay balancing in HDL Coder, see Delay Balancing (R2024b).

Improved distributed pipelining through the clock-rate pipelining hierarchy

Prior to R2024b, distributed pipelining could not distribute pipelines across multiple clock-rate pipelining (CRP) regions located at different levels of the subsystem hierarchy. The hierarchical arrangement provided suboptimal distributed pipelining and clock-rate pipelining performance by creating longer combinatorial paths that distributed pipelining could not optimize. To achieve better results from distributed pipelining in conjunction with clock-rate pipelining, you had to use hierarchy flattening to remove the presence of hierarchy during optimizations. However, this method can reduce the readability of both the generated model and HDL code by creating fewer and larger subsystems.

Starting in R2024b, distributed pipelining can optimize across multiple clock-rate pipelining regions within the hierarchy, eliminating the need to request hierarchy flattening. You can expect an automatic improvement in the quality of results without special modifications.

Additionally, distributed pipelining now always operates with the Pipeline

distribution priority parameter set to

Performance for clock-rate pipelining regions, even if

the global Pipeline distribution priority parameter is set to

numerical integrity. Since clock-rate pipelining regions

effectively have a slower data rate that is sampled by zero order holds, clock-rate

initialization cycle mismatches are not at risk, even when you use performance mode.

Distributed pipelining no longer considers certain blocks as blockers for the

optimization inside clock-rate pipelining regions, such as NOT operation or Lookup

tables.

This table compares the results of toggling hierarchy flattening on and off for a model that uses distributed pipelining and clock-rate pipelining in R2024a and R2024b.

| Metric | Flattening Off (R2024a) | Flattening On (R2204a) | Flattening Off (R2024b) | Flattening On (R2024b) |

|---|---|---|---|---|

| 1-bit Registers | 2279 | 4739 | 1452 | 1292 |

| Estimated critical path (ns) | 29.5 | 19.9 | 15.1 | 12.3 |

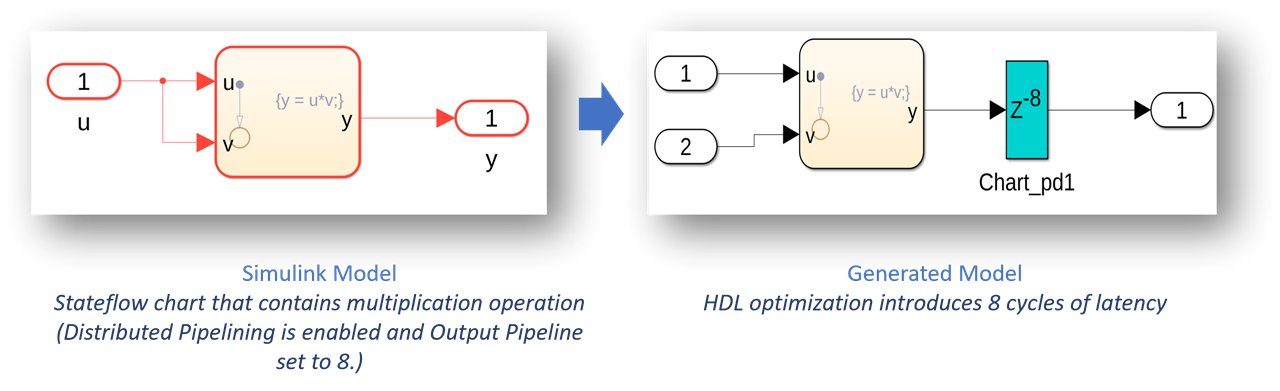

I/O Optimizations

Use design delays inside the frame-to-sample algorithm

Reduce the complexity of your frame-to-sample algorithm models by using design delays inside the frame-to-sample algorithm. Starting in R2024b, you can:

Use Unit Delay and Integer Delay blocks inside the frame-to-sample design under test (DUT) subsystem. The delays can be of any length and must not be enabled or resettable.

Use persistent variables to create unit and variable integer design delays in MATLAB Function blocks inside the frame-to-sample DUT subsystem.

Use the Delay size threshold for external memory (bits) model configuration parameter to map design delays to external memory. The parameter can be found in the Configuration Parameters window, in the HDL Code Generation > Optimization pane, click the Frame to Sample Conversion tab.

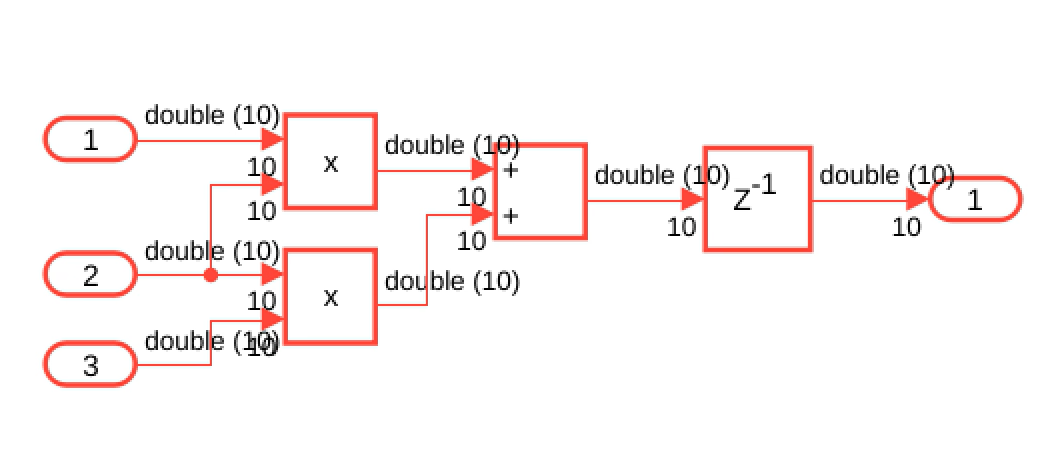

For example, this image shows the optical flow algorithm with the design delay outside the frame-to-sample DUT and the design delay inside the frame-to-sample DUT. Prior to R2024b, you modeled the current frame and the previous frame. In R2024b you model only the current frame and use a design delay inside the frame-to-sample DUT to represent the previous frame. The frame delays are mapped to external random access memory (RAM). See Generate HDL Code from Frame-Based Models by Using Neighborhood Modeling Methods (R2024b).

Exclude functions from fixed-point conversion with

coder.float2fixed.skip

Use the new coder.float2fixed.skip (R2024b) pragma to

designate functions that you do not want to convert to fixed point when using the

-float2fixed option with the codegen (R2024b)

command.

To exclude a function from fixed-point conversion, specify the function as a cell

array input to the pragma at the beginning of the code to be converted. You can specify

both custom and built-in functions. For example, exclude exp from

fixed-point conversion in designFunc, defined below.

function out = designFunc(inp) coder.float2fixed.skip({'exp'}); out = exp(inp); [...] end

Use 3-D matrices input for the neighborhood processing in frame-to-sample conversion

You can now perform neighborhood processing and element-wise or iterative operations on RGB images or 3-D matrices to generate synthesizable HDL code using the frame-to-sample conversion. You can use 3-D matrices as inputs for these neighborhood processing functions and blocks when you use the frame-to-sample conversion algorithm:

hdl.npufun (R2024b)

hdl.iteratorfun (R2024b)

Neighborhood Processing Subsystem (R2024b)

When you pass a 3-D matrix to the hdl.npufun function, the

function executes the kernel function on each sliding window in the input data. For each

plane of the 3-D matrix, the function carries out the sliding window operation based on

the defined kernel size. The function then maps the output of the kernel operation for

each plane to the corresponding pixels in that plane. See HDL Code Generation from Frame-Based Algorithms (R2024b).

For example, perform the neighborhood processing algorithm to perform blurring operation on RGB image.

I_out = hdl.npufun(@blurringKernel, [5 5], I); function y = blurringKernel(N) out_R = sum(reshape(N(:,:,1)/25,[],1)); out_G = sum(reshape(N(:,:,2)/25,[],1)); out_B = sum(reshape(N(:,:,3)/25,[],1)); y = [out_R out_G out_B]; end

Use persistent variables with the hdl.npufun kernel function

during frame-to-sample optimization with multiple samples per cycle

During the frame-to-sample optimization, you can now use persistent variables in the

hdl.npufun (R2024b) kernel function when generating code with multiple samples

per cycle. Previously, you could use persistent variable only when generating code with

one sample per cycle.

To use persistent variables in hdl.npufun function, in the

Configuration Parameters dialog, set:

Input processing order to

RowMajorSamples per cycle to any value

Support for non-integer boundary constants in hdl.npufun

When using the hdl.npufun (R2024b) function, you can now specify the

BoundaryConstant argument value as a numeric scalar.

Previously, you could specify the value as an integer scalar only.

High-Level Synthesis Code Generation

Generate HLS code generation in row-major array layout

Starting from R2024b, you can choose to generate HLS code that uses row-major array layout. Row-major array layout can improve performance for certain algorithms and ease integration with other code that also uses row-major layout. Previously, the code generator produced HLS code using column-major array layout by default.

Consider the MATLAB function foo, which adds two vectors and returns the

sum.

% MATLAB code function y = foo(x) A = [1 2 3; 4 5 6]; y = A + x; end % MATLAB test bench x = [7 8 9; 10 11 12]; y = foo(x);

| Code Generation Commands | Generated HLS code |

|---|---|

MATLAB command to generate HLS code in row-major array layout. cfg = coder.config('hdl'); cfg.Workflow = "High Level Synthesis"; cfg.TestBenchName = "foo_tb"; cfg.RowMajor = true; codegen foo -config cfg -report |

class fooClass

{

public:

void foo(real_T x[2][3], real_T y[2][3])

{

static real_T t_2[2][3]={{1.0, 2.0, 3.0},{4.0, 5.0, 6.0}};

L1:

for (int32_T t_1 = 0; t_1 < 2; t_1 = t_1 + 1) {

L2:

for (int32_T t_0 = 0; t_0 < 3; t_0 = t_0 + 1) {

y[t_1][t_0] = t_2[t_1][t_0] + x[t_1][t_0];

}

}

}

}; |

MATLAB command to generate HLS code in column-major array layout. cfg = coder.config('hdl'); cfg.Workflow = "High Level Synthesis"; cfg.TestBenchName = "foo_tb"; cfg.RowMajor = false; codegen foo -config cfg -report |

class fooClass

{

public:

void foo(real_T x[3][2], real_T y[3][2])

{

static real_T A[3][2]={{1.0, 4.0},{2.0, 5.0},{3.0, 6.0}};

L1:

for (int32_T t_1 = 0; t_1 < 3; t_1 = t_1 + 1) {

L2:

for (int32_T t_0 = 0; t_0 < 2; t_0 = t_0 + 1) {

y[t_1][t_0] = x[t_1][t_0] + A[t_1][t_0];

}

}

}

}; |

Improvements in the HLS code generation workflow

Starting in R2024b, the HLS code generation workflow supports:

coder.hdl.literaltext(R2024b) pragma, which embeds custom pragma statements in the generated HLS code as:coder.hdl.literaltext("pragma statement");Structures as inputs and outputs at the top-level DUT ports for HLS code generation.

Arrays of structures as local variables inside the MATLAB design, but not at the inputs and outputs of the entry-point function.

ULP error FP tolerance strategy to handle floating-point tolerance errors during simulation of the generated HLS code. See, Tolerance Value (R2024b).

SaturateOnIntegerOverflowconfiguration option to handle integer overflow.External code integration. For more information, see Call Custom HLS Code from the Generated HLS Code (R2024b).

IP Core Generation and Hardware Deployment

Generate HDL code with AMD floating-point libraries for Xilinx devices

In R2024b, you can create designs and generate HDL code that utilizes the AMD floating-point library IPs. When you set the Synthesis Tool (R2024b) model

configuration parameter to Xilinx Vivado, you can set the

Vendor Specific Floating Point Library (R2024b) configuration

parameter to AMDFloatingPointOperators, which enables the

generation of code that incorporates both AMD floating-point IP blocks and HDL Coder native floating-point IP blocks.

See Generate HDL Code Using HDL Coder Native Floating Point and AMD Floating Point Library IP (R2024b).

Because the AMD floating-point IP blocks are optimized for synthesis, you can map them to FPGA resources, including hardened DSP floating-point adder and multiplier (DSPFP32) primitives on Xilinx Versal devices. For other Xilinx device families, the generated HDL code uses the full DSP mode of the AMD floating-point operator. You can use this mixed-design approach to accommodate larger and more complex designs into the FPGA fabric. You can use this hybrid design with AMD floating-point libraries on Xilinx devices such as Versal, Zynq® UltraScale+™, and more. See hdlcoder.FloatingPointTargetConfig (R2024b).

In the HDL Workflow Advisor, you can generate the HDL code and IP core for your design with AMD floating-point IPs using the IP core generation workflow. You can also use the AMD floating-point library when you use the generic ASIC/FPGA workflow.

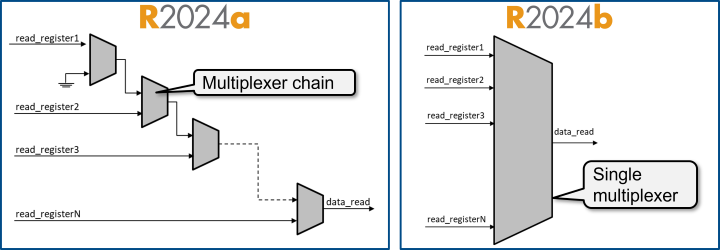

Optimize register interface timing by improving the read address decoder architecture

Prior to R2024b, mapping a large number of read registers to AXI4 or AXI4-Lite

interfaces when generating an IP core results in a long multiplexer chain that impacts

the maximum IP core frequency. Using the

AXI4SlavePortToPipelineRegisterRatio parameter to achieve the

target frequency, leads to a quadratic increase in resource usage due to the increase in

number of registers. In R2024b, HDL Coder replaces the long multiplexer chain with a single-case statement, which

improves the read address decoder critical path. See Optimize Timing on Register Interface (R2024b).

To control the structure of the read address decoder, use the Register interface read pipeline parameter in task 3.2 Generate RTL Code and IP Core of the HDL Workflow Advisor. Alternatively, use the Register interface read pipeline parameter in the Interface Settings tab of the IP Core Editor. During IP core generation, HDL Coder creates a multiplexer tree that distributes the specified pipeline registers. This image compares the address decoder architecture in R2024b and prior releases.

See The AXI4SlavePortToPipelineRegisterRatio HDL block property has been removed.

Upgrade to Intel Quartus Pro 23.3

HDL Coder now supports Intel Quartus Pro 23.3.

For more information about supported synthesis tools, see HDL Language Support and Supported Third-Party Tools and Hardware (R2024b).

Upgrade to Microchip Libero SoC 2023.2

HDL Coder now supports Microchip Libero SoC 2023.2.

For more information about supported synthesis tools, see HDL Language Support and Supported Third-Party Tools and Hardware (R2024b).

Map ports with complex data types to AXI and AXI-4 Lite interfaces

In R2024b, you can now map ports with complex data types to the AXI4 and AXI4-Lite interfaces.

For more information about mapping ports, see Map Complex Data Types to AXI4 Slave Interface (R2024b).

Support for Cadence Genus when generating custom synthesis workflows for Generic ASIC/FPGA devices

In R2024b, HDL Coder supports Cadence Genus when using a custom synthesis workflow and targeting generic ASIC/FPGA devices.

For more information about custom synthesis workflows, see ASIC Synthesis and Analysis Overview (R2024b).

Additional options for configuring hardware with the HDL Coder Support Package for Intel FPGA and SoC Devices

If you have the HDL Coder Support Package for Intel FPGA and SoC Devices (R2024b), you can now use the Hardware Setup Wizard to do these tasks:

Verify Ethernet connectivity on the host machine and check for an SD card reader and a writable SD card.

Choose the available hardware board within the support package.

Select between automatic or manual modes for downloading required third-party tools.

Install the Intel SoC FPGA Embedded Development Suite (EDS) tool for deploying and running Linux® ARM® applications on the Intel SoC Board.

Identify the SD card drive and write the firmware image to it.

Configure the hardware connections and adjust the jumper settings appropriately.

Confirm the hardware's connection to the host computer.

For more information, see Guided Hardware Setup (R2024b).

Download required third-party tools when configuring hardware

You can now automatically or manually download and install third-party tools for your board when you use the Hardware Setup Wizard in the HDL Coder Support Package for Xilinx FPGA and SoC Devices.

When you set Download Mode to

Automatic, the wizard downloads and installs the

necessary third-party tools from the internet to your host computer, which must have

internet connectivity.

For host computers without internet access, you can set Download Mode to Manual to manually download the third-party tools. The wizard provides step-by-step instructions for downloading the required third-party tools. You can use another computer with internet access to download these tools and then transfer and install them on your host computer.

For more information, see Guided Hardware Setup (R2024b).

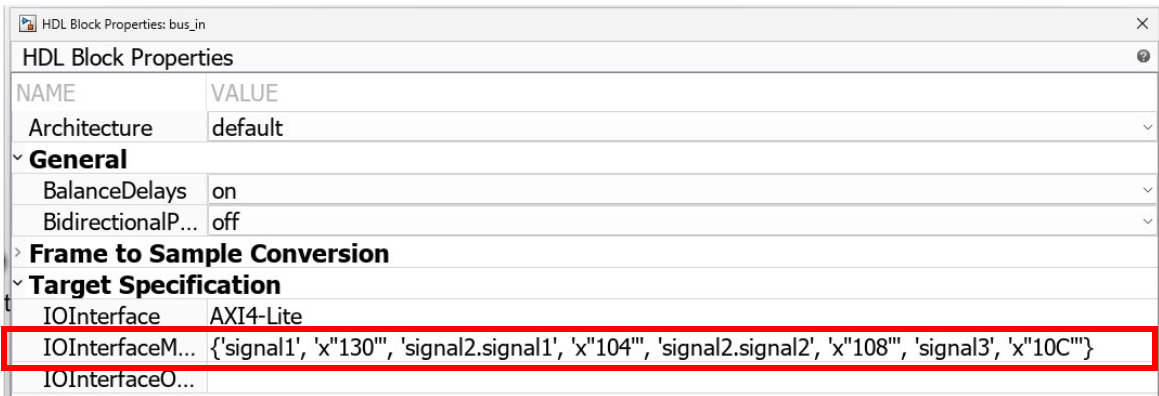

View and edit bus element addresses in bus-mapped Inport and Outport blocks

Starting in R2024b, HDL Coder saves the address assignments for each bus element to the bus-mapped

Inport and Outport blocks in the design under test

(DUT) to the IOInterfaceMapping HDL block property. Use the

IOInterfaceMapping property or the

hdlset_param function to view and edit the address for any of

the bus elements.

When you use the Target platform interface table in the Interface Mapping tab of the IP Core Editor or in task 1.3 Set Target Interface of the HDL Workflow Advisor, you still can view and edit only the address of the first bus element.

Define Custom Board and Reference Design for Zynq Ultrascale+ MPSoC Workflow

The Define Custom Board and Reference Design for Zynq Ultrascale+ MPSoC Workflow example shows you how to define and register a custom board and reference design for the Zynq UltraScale+ platforms. This example shows the workflow for the Xilinx Zynq UltraScale+ MPSoC ZCU104 evaluation kit in HDL Workflow Advisor.

For more information, see Define Custom Board and Reference Design for Zynq Ultrascale+ MPSoC Workflow (R2024b).

Functionality being removed or changed

The AXI4SlavePortToPipelineRegisterRatio HDL block property has been removed

Errors

The AXI4SlavePortToPipelineRegisterRatio HDL block parameter has been removed. Use the RegisterInterfaceReadPipeline HDL block parameter instead. If you open a model created in R2024a or earlier, HDL Coder ignores the value of the AXI4SlavePortToPipelineRegisterRatio HDL block parameter during IP core generation.

The IP repository parameter has been removed

The IP repository parameter has been removed from task 3.2 Generate RTL Code and IP Core and the General tab of the IP Core Editor.

The IPCoreRepository parameter will be removed

The IPCoreRepository property of the

hdlcoder.WorkflowConfig object will be deprecated in a future

release. To copy the generated IP core into an IP repository folder, use the

copyfile (R2024b) function.

Simscape Hardware-in-the-Loop Workflow

Simscape HDL Workflow Advisor: Improved fixed-point data type support

The fixed-point data type precision is now supported for Simscape models containing nonlinear Simscape networks. To learn more about how to decide on using fixed-point data types for your plant models, see Use Fixed-Point Precision (R2024b).

Previously, only linear Simscape networks supported fixed-point data type precision.

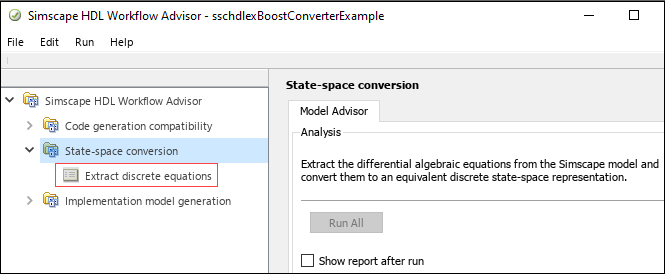

Simscape HDL Workflow Advisor: Simscape network selection for FPGA deployment

You can now generate a Simulink state-space equivalent model for any desired Simscape network of your plant model while retaining the additional networks in their original forms. This enhancement helps to effectively use the resources on FPGA boards by enabling you to select only the network that you want to deploy on the hardware and not the entire model. This functionality enables optimization of HDL code for hybrid plant models (containing Simulink and Simscape blocks).

Previously, you could generate a state-space equivalent only for the entire model.

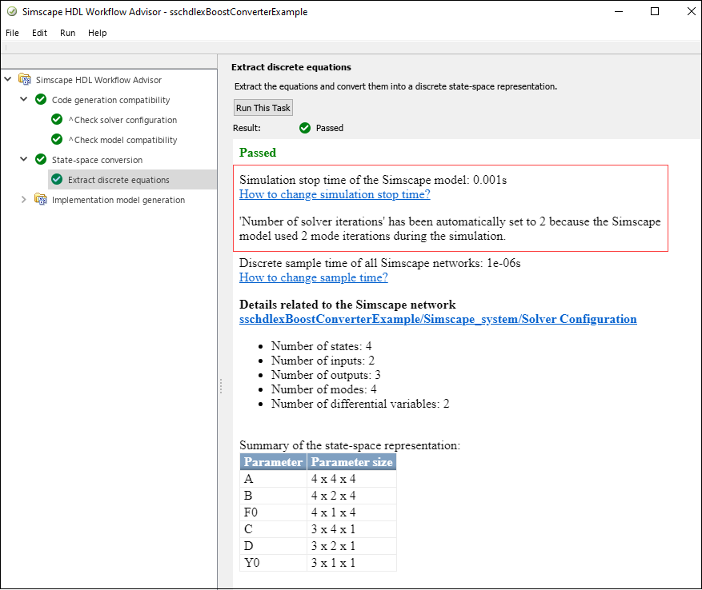

For example, consider sschdlexBoostConverterMultiNetModel model. In

this model, you can select the FPGA Subsystem block and generate a state-space

equivalent for it.

To generate a state-space equivalent for the FPGA Subsystem, open the Simscape HDL

Workflow Advisor for it by running the sschdladvisor (R2024b) function at the MATLAB command prompt.

sschdladvisor("sschdlexBoostConverterMultiNetModel/FPGA Subsystem")

For more information, see Open Advisor for Subsystem (R2024b).

Tune run-time parameter values for multi-network Simscape models

The Simscape hardware-in-the-loop (HIL) workflow now supports parameter tuning for

Simscape models containing multiple Simscape networks. You can modify the run-time parameter values in the generated

FPGA bitstream for all the networks in the model. You can

fine-tune the parameter values of these networks without rerunning the synthesis for the

generated HDL implementation models. For more information, see sschdl.updateRuntimeParameters (R2024b).

Previously, you could tune Simscape run-time parameters only for Simscape models containing a single Simscape network.

Automatically replace Simscape components with optimized equivalents for FPGA deployment

Additional Simscape components are now supported for automatic replacement:

PMSM (R2024b) (Simscape Electrical)— You can now automatically replace Simscape PMSM block with an equivalent optimized PMSM block in your Simscape model and tune the run-time parameters. You can use this block to optimize your Simscape model and generate HDL code by using the Backward Euler and Trapezoidal Rule local solvers.

By using a Simulink PMSM block, you can: